Si4063 revC2A Command/Property API Documentation

Interface Version: 1.0

Document Version: 2.0.5

Generated: 2015-03-18T10:15:42-05:00

Introduction

This document provides API descriptions for the commands and properties used

to control and configure the part. The interface version tracks any functional

changes to the API (command, property, field, enumeration, etc.). The documentation

version tracks any text changes to the summary or description text of the API

components.

The commands are listed in a summary table with links to command details.

The properties are listed in a summary

table with links to property details. The feature available column in the

summary tables lists the firmware revision which first implemented the command

or property.

An entry in the summary table will link

to a details section, which contains a register view with fields. Clicking a

field in the register view will auto-expand the corresponding field details.

An up button in the field detail links back to the register view. Each

register view title links back to the summary table entry. These hyper-links

provide two-click access from top to bottom.

Command Summary

| COMMON_COMMANDS | ||||

|---|---|---|---|---|

| Number | Name | Summary | Feature Available | |

| 0x00 | NOP | No Operation command. | ||

| 0x01 | PART_INFO | Reports basic information about the device. | ||

| 0x10 | FUNC_INFO | Returns the Function revision information of the device. | ||

| 0x11 | SET_PROPERTY | Sets the value of one or more properties. | ||

| 0x12 | GET_PROPERTY | Retrieves the value of one or more properties | ||

| 0x13 | GPIO_PIN_CFG | Configures the GPIO pins. | ||

| 0x15 | FIFO_INFO | Access the current byte counts in the TX and RX FIFOs, and provide for resetting the FIFOs. | ||

| 0x20 | GET_INT_STATUS | Returns the interrupt status of ALL the possible interrupt events (both STATUS and PENDING). Optionally, it may be used to clear latched (PENDING) interrupt events. | ||

| 0x33 | REQUEST_DEVICE_STATE | Request current device state and channel. | ||

| 0x34 | CHANGE_STATE | Manually switch the chip to a desired operating state. | ||

| 0x44 | READ_CMD_BUFF | Used to read CTS and the command response. | ||

| 0x50 | FRR_A_READ | Reads the fast response registers (FRR) starting with FRR_A. | ||

| 0x51 | FRR_B_READ | Reads the fast response registers (FRR) starting with FRR_B. | ||

| 0x53 | FRR_C_READ | Reads the fast response registers (FRR) starting with FRR_C. | ||

| 0x57 | FRR_D_READ | Reads the fast response registers (FRR) starting with FRR_D. | ||

| TX_COMMANDS | ||||

|---|---|---|---|---|

| Number | Name | Summary | Feature Available | |

| 0x31 | START_TX | Switches to TX state and starts transmission of a packet. | ||

| 0x66 | WRITE_TX_FIFO | Writes data byte(s) to the TX FIFO. | ||

| ADVANCED_COMMANDS | ||||

|---|---|---|---|---|

| Number | Name | Summary | Feature Available | |

| 0x14 | GET_ADC_READING | Performs conversions using the Auxiliary ADC and returns the results of those conversions. | ||

| 0x21 | GET_PH_STATUS | Returns the interrupt status of the Packet Handler Interrupt Group (both STATUS and PENDING). Optionally, it may be used to clear latched (PENDING) interrupt events. | ||

| 0x23 | GET_CHIP_STATUS | Returns the interrupt status of the Chip Interrupt Group (both STATUS and PENDING). Optionally, it may be used to clear latched (PENDING) interrupt events. | ||

Property Summary

| GLOBAL (0x00) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x00 | 0x00 | GLOBAL_XO_TUNE | 0x40 | Configure the internal capacitor frequency tuning bank for the crystal oscillator. | ||

| 0x00 | 0x01 | GLOBAL_CLK_CFG | 0x00 | Clock configuration options. | ||

| 0x00 | 0x02 | GLOBAL_LOW_BATT_THRESH | 0x18 | Configures the threshold voltage for low-battery detection. | ||

| 0x00 | 0x03 | GLOBAL_CONFIG | 0x20 | Global configuration settings. | ||

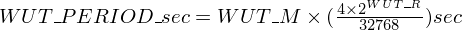

| 0x00 | 0x04 | GLOBAL_WUT_CONFIG | 0x00 | General Wakeup Timer feature configuration. | ||

| 0x00 | 0x05 0x06 |

GLOBAL_WUT_M | 0x00 0x01 |

Configure the mantissa of the Wake-Up Timer (WUT) value. | ||

| 0x00 | 0x07 | GLOBAL_WUT_R | 0x60 | Configure the exponent of the Wake-Up Timer (WUT) value. | ||

| 0x00 | 0x08 | GLOBAL_WUT_LDC | 0x00 | Configures the period of time the chip remains active after automatic wake-up in LDC mode. | ||

| 0x00 | 0x09 | GLOBAL_WUT_CAL | 0x00 | Controls if calibration of the 32K R-C Oscillator will be performed on intervals of the WUT. | ||

| INT_CTL (0x01) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x01 | 0x00 | INT_CTL_ENABLE | 0x04 | This property provides for global enabling of the three interrupt groups (Chip, Modem and Packet Handler) in order to generate HW interrupts at the NIRQ pin. | ||

| 0x01 | 0x01 | INT_CTL_PH_ENABLE | 0x00 | Enable individual interrupt sources within the Packet Handler Interrupt Group to generate a HW interrupt on the NIRQ output pin. | ||

| 0x01 | 0x03 | INT_CTL_CHIP_ENABLE | 0x04 | Enable individual interrupt sources within the Chip Interrupt Group to generate a HW interrupt on the NIRQ output pin. | ||

| FRR_CTL (0x02) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x02 | 0x00 | FRR_CTL_A_MODE | 0x01 | Fast Response Register A Configuration. | ||

| 0x02 | 0x01 | FRR_CTL_B_MODE | 0x02 | Fast Response Register B Configuration. | ||

| 0x02 | 0x02 | FRR_CTL_C_MODE | 0x09 | Fast Response Register C Configuration. | ||

| 0x02 | 0x03 | FRR_CTL_D_MODE | 0x00 | Fast Response Register D Configuration. | ||

| PREAMBLE (0x10) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x10 | 0x00 | PREAMBLE_TX_LENGTH | 0x08 | Configure length of TX Preamble. | ||

| 0x10 | 0x01 | PREAMBLE_CONFIG_STD_1 | 0x14 | Configuration of reception of a packet with a Standard Preamble pattern. | ||

| 0x10 | 0x02 | PREAMBLE_CONFIG_NSTD | 0x00 | Configuration of transmission/reception of a packet with a Non-Standard Preamble pattern. | ||

| 0x10 | 0x04 | PREAMBLE_CONFIG | 0x21 | General configuration bits for the Preamble field. | ||

| 0x10 | 0x05 0x06 0x07 0x08 |

PREAMBLE_PATTERN | 0x00 0x00 0x00 0x00 |

Configuration of the bit values describing a Non-Standard Preamble pattern. | ||

| SYNC (0x11) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x11 | 0x00 | SYNC_CONFIG | 0x01 | Sync Word configuration bits. | ||

| 0x11 | 0x01 0x02 0x03 0x04 |

SYNC_BITS | 0x2d 0xd4 0x2d 0xd4 |

Sync word. | ||

| 0x11 | 0x05 | SYNC_CONFIG2 | 0x00 | Sync Word configuration bits. | ||

| PKT (0x12) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x12 | 0x00 | PKT_CRC_CONFIG | 0x00 | Select a CRC polynomial and seed. | ||

| 0x12 | 0x01 0x02 |

PKT_WHT_POLY | 0x01 0x08 |

16-bit polynomial value for the PN Generator (e.g., for Data Whitening) | ||

| 0x12 | 0x03 0x04 |

PKT_WHT_SEED | 0xff 0xff |

16-bit seed value for the PN Generator (e.g., for Data Whitening) | ||

| 0x12 | 0x05 | PKT_WHT_BIT_NUM | 0x00 | Selects which bit of the LFSR (used to generate the PN / data whitening sequence) is used as the output bit for data scrambling. | ||

| 0x12 | 0x06 | PKT_CONFIG1 | 0x00 | General configuration bits for transmission or reception of a packet. | ||

| 0x12 | 0x07 | PKT_CONFIG2 | 0x00 | General packet configuration bits. | ||

| 0x12 | 0x0b | PKT_TX_THRESHOLD | 0x30 | TX FIFO almost empty threshold. | ||

| 0x12 | 0x0d 0x0e |

PKT_FIELD_1_LENGTH | 0x00 0x00 |

Unsigned 13-bit Field 1 length value. | ||

| 0x12 | 0x0f | PKT_FIELD_1_CONFIG | 0x00 | General data processing and packet configuration bits for Field 1. | ||

| 0x12 | 0x10 | PKT_FIELD_1_CRC_CONFIG | 0x00 | Configuration of CRC control bits across Field 1. | ||

| 0x12 | 0x11 0x12 |

PKT_FIELD_2_LENGTH | 0x00 0x00 |

Unsigned 13-bit Field 2 length value. | ||

| 0x12 | 0x13 | PKT_FIELD_2_CONFIG | 0x00 | General data processing and packet configuration bits for Field 2. | ||

| 0x12 | 0x14 | PKT_FIELD_2_CRC_CONFIG | 0x00 | Configuration of CRC control bits across Field 2. | ||

| 0x12 | 0x15 0x16 |

PKT_FIELD_3_LENGTH | 0x00 0x00 |

Unsigned 13-bit Field 3 length value. | ||

| 0x12 | 0x17 | PKT_FIELD_3_CONFIG | 0x00 | General data processing and packet configuration bits for Field 3. | ||

| 0x12 | 0x18 | PKT_FIELD_3_CRC_CONFIG | 0x00 | Configuration of CRC control bits across Field 3. | ||

| 0x12 | 0x19 0x1a |

PKT_FIELD_4_LENGTH | 0x00 0x00 |

Unsigned 13-bit Field 4 length value. | ||

| 0x12 | 0x1b | PKT_FIELD_4_CONFIG | 0x00 | General data processing and packet configuration bits for Field 4. | ||

| 0x12 | 0x1c | PKT_FIELD_4_CRC_CONFIG | 0x00 | Configuration of CRC control bits across Field 4. | ||

| 0x12 | 0x1d 0x1e |

PKT_FIELD_5_LENGTH | 0x00 0x00 |

Unsigned 13-bit Field 5 length value. | ||

| 0x12 | 0x1f | PKT_FIELD_5_CONFIG | 0x00 | General data processing and packet configuration bits for Field 5. | ||

| 0x12 | 0x20 | PKT_FIELD_5_CRC_CONFIG | 0x00 | Configuration of CRC control bits across Field 5. | ||

| MODEM (0x20) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x20 | 0x00 | MODEM_MOD_TYPE | 0x02 | Selects the type of modulation. In TX mode, additionally selects the source of the modulation. | ||

| 0x20 | 0x01 | MODEM_MAP_CONTROL | 0x80 | Controls polarity and mapping of transmit and receive bits. | ||

| 0x20 | 0x02 | MODEM_DSM_CTRL | 0x07 | Miscellaneous control bits for the Delta-Sigma Modulator (DSM) in the PLL Synthesizer. | ||

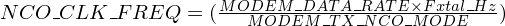

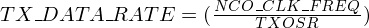

| 0x20 | 0x03 0x04 0x05 |

MODEM_DATA_RATE | 0x0f 0x42 0x40 |

Unsigned 24-bit value used to determine the TX data rate | ||

| 0x20 | 0x06 0x07 0x08 0x09 |

MODEM_TX_NCO_MODE | 0x01 0xc9 0xc3 0x80 |

TX Gaussian filter oversampling ratio and Byte 3 of unsigned 26-bit TX Numerically Controlled Oscillator (NCO) modulus. | ||

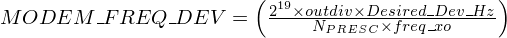

| 0x20 | 0x0a 0x0b 0x0c |

MODEM_FREQ_DEV | 0x00 0x06 0xd3 |

17-bit unsigned TX frequency deviation word. | ||

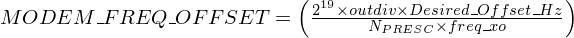

| 0x20 | 0x0d 0x0e |

MODEM_FREQ_OFFSET | 0x00 0x00 |

Frequency offset adjustment (a 16-bit signed number). | ||

| 0x20 | 0x0f | MODEM_TX_FILTER_COEFF_8 | 0x67 | The 8th coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x10 | MODEM_TX_FILTER_COEFF_7 | 0x60 | The 7th coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x11 | MODEM_TX_FILTER_COEFF_6 | 0x4d | The 6th coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x12 | MODEM_TX_FILTER_COEFF_5 | 0x36 | The 5th coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x13 | MODEM_TX_FILTER_COEFF_4 | 0x21 | The 4th coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x14 | MODEM_TX_FILTER_COEFF_3 | 0x11 | The 3rd coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x15 | MODEM_TX_FILTER_COEFF_2 | 0x08 | The 2nd coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x16 | MODEM_TX_FILTER_COEFF_1 | 0x03 | The 1st coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x17 | MODEM_TX_FILTER_COEFF_0 | 0x01 | The 0th coefficient of TX spectral shaping filter. | ||

| 0x20 | 0x18 | MODEM_TX_RAMP_DELAY | 0x01 | TX ramp-down delay setting. | ||

| 0x20 | 0x19 | MODEM_MDM_CTRL | 0x00 | MDM control. | ||

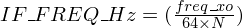

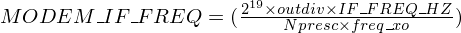

| 0x20 | 0x1a | MODEM_IF_CONTROL | 0x08 | Selects Fixed-IF, Scaled-IF, or Zero-IF mode of RX Modem operation. | ||

| 0x20 | 0x1b 0x1c 0x1d |

MODEM_IF_FREQ | 0x03 0xc0 0x00 |

the IF frequency setting (an 18-bit signed number). | ||

| 0x20 | 0x1e | MODEM_DECIMATION_CFG1 | 0x10 | Specifies three decimator ratios for the Cascaded Integrator Comb (CIC) filter. | ||

| 0x20 | 0x1f | MODEM_DECIMATION_CFG0 | 0x20 | Specifies miscellaneous parameters and decimator ratios for the Cascaded Integrator Comb (CIC) filter. | ||

| 0x20 | 0x20 | MODEM_DECIMATION_CFG2 | 0x00 | Specifies miscellaneous decimator filter selections. | ||

| 0x20 | 0x21 | MODEM_IFPKD_THRESHOLDS | 0xe8 | |||

| 0x20 | 0x22 0x23 |

MODEM_BCR_OSR | 0x00 0x4b |

RX BCR/Slicer oversampling rate (12-bit unsigned number). | ||

| 0x20 | 0x24 0x25 0x26 |

MODEM_BCR_NCO_OFFSET | 0x06 0xd3 0xa0 |

RX BCR NCO offset value (an unsigned 22-bit number). | ||

| 0x20 | 0x27 0x28 |

MODEM_BCR_GAIN | 0x06 0xd3 |

The unsigned 11-bit RX BCR loop gain value. | ||

| 0x20 | 0x29 | MODEM_BCR_GEAR | 0x02 | RX BCR loop gear control. | ||

| 0x20 | 0x2a | MODEM_BCR_MISC1 | 0xc0 | Miscellaneous control bits for the RX BCR loop. | ||

| 0x20 | 0x2b | MODEM_BCR_MISC0 | 0x00 | Miscellaneous RX BCR loop controls. | ||

| 0x20 | 0x2c | MODEM_AFC_GEAR | 0x00 | RX AFC loop gear control. | ||

| 0x20 | 0x2d | MODEM_AFC_WAIT | 0x23 | RX AFC loop wait time control. | ||

| 0x20 | 0x2e 0x2f |

MODEM_AFC_GAIN | 0x83 0x69 |

Sets the gain of the PLL-based AFC acquisition loop, and provides miscellaneous control bits for AFC functionality. | ||

| 0x20 | 0x30 0x31 |

MODEM_AFC_LIMITER | 0x00 0x40 |

Set the AFC limiter value. | ||

| 0x20 | 0x32 | MODEM_AFC_MISC | 0xa0 | Specifies miscellaneous AFC control bits. | ||

| 0x20 | 0x33 | MODEM_AFC_ZIFOFF | 0x00 | AFC fixed frequency offset in zero IF mode. | ||

| 0x20 | 0x34 | MODEM_ADC_CTRL | 0x00 | Sigma Delta ADC controls. | ||

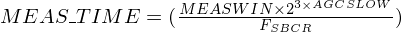

| 0x20 | 0x35 | MODEM_AGC_CONTROL | 0xe0 | Miscellaneous control bits for the Automatic Gain Control (AGC) function in the RX Chain. | ||

| 0x20 | 0x38 | MODEM_AGC_WINDOW_SIZE | 0x11 | Specifies the size of the measurement and settling windows for the AGC algorithm. | ||

| 0x20 | 0x39 | MODEM_AGC_RFPD_DECAY | 0x10 | Sets the decay time of the RF peak detectors. | ||

| 0x20 | 0x3a | MODEM_AGC_IFPD_DECAY | 0x10 | Sets the decay time of the IF peak detectors. | ||

| 0x20 | 0x3b | MODEM_FSK4_GAIN1 | 0x0b | Specifies the gain factor of the secondary branch in 4(G)FSK ISI-suppression. | ||

| 0x20 | 0x3c | MODEM_FSK4_GAIN0 | 0x1c | Specifies the gain factor of the primary branch in 4(G)FSK ISI-suppression. | ||

| 0x20 | 0x3d 0x3e |

MODEM_FSK4_TH | 0x40 0x00 |

16 bit 4(G)FSK slicer threshold. | ||

| 0x20 | 0x3f | MODEM_FSK4_MAP | 0x00 | 4(G)FSK symbol mapping code. | ||

| 0x20 | 0x40 | MODEM_OOK_PDTC | 0x2b | Configures the attack and decay times of the OOK Peak Detector. | ||

| 0x20 | 0x41 | MODEM_OOK_BLOPK | 0x0c | Configures the slicing reference level of the OOK Peak Detector. | ||

| 0x20 | 0x42 | MODEM_OOK_CNT1 | 0xa4 | OOK control. | ||

| 0x20 | 0x43 | MODEM_OOK_MISC | 0x03 | Selects the detector(s) used for demodulation of an OOK signal, or for demodulation of a (G)FSK signal when using the asynchronous demodulator. | ||

| 0x20 | 0x45 | MODEM_RAW_CONTROL | 0x02 | Defines gain and enable controls for raw / nonstandard mode. | ||

| 0x20 | 0x46 0x47 |

MODEM_RAW_EYE | 0x00 0xa3 |

11 bit eye-open detector threshold. | ||

| 0x20 | 0x50 | MODEM_RAW_SEARCH2 | 0x00 | Defines and controls the search period length for the Moving Average and Min-Max detectors. | ||

| 0x20 | 0x51 | MODEM_CLKGEN_BAND | 0x08 | Select PLL Synthesizer output divider ratio as a function of frequency band. | ||

| 0x20 | 0x54 | MODEM_SPIKE_DET | 0x00 | Configures the threshold for (G)FSK Spike Detection. | ||

| PA (0x22) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x22 | 0x00 | PA_MODE | 0x08 | Selects the PA operating mode, and selects resolution of PA power adjustment (i.e., step size). | ||

| 0x22 | 0x01 | PA_PWR_LVL | 0x7f | Configuration of PA output power level. | ||

| 0x22 | 0x02 | PA_BIAS_CLKDUTY | 0x00 | Configuration of the PA Bias and duty cycle of the TX clock source. | ||

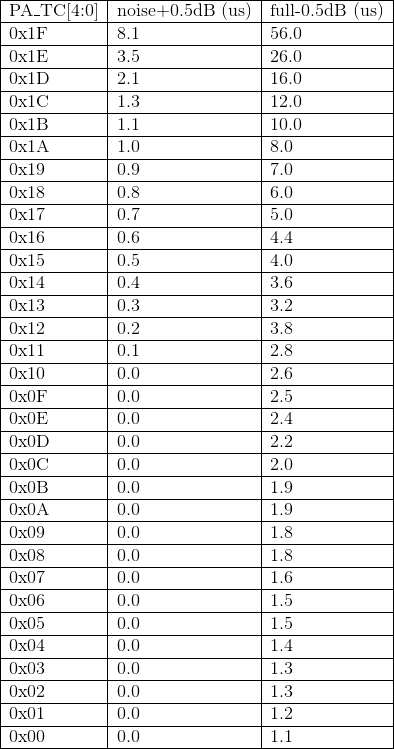

| 0x22 | 0x03 | PA_TC | 0x5d | Configuration of PA ramping parameters. | ||

| 0x22 | 0x04 | PA_RAMP_EX | 0x80 | Select the time constant of the external PA ramp signal. | ||

| 0x22 | 0x05 | PA_RAMP_DOWN_DELAY | 0x23 | Delay from the start of the PA ramp down to disabling of the PA output. | ||

| SYNTH (0x23) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0x23 | 0x00 | SYNTH_PFDCP_CPFF | 0x2c | Feed forward charge pump current selection. | ||

| 0x23 | 0x01 | SYNTH_PFDCP_CPINT | 0x0e | Integration charge pump current selection. | ||

| 0x23 | 0x02 | SYNTH_VCO_KV | 0x0b | Gain scaling factors (Kv) for the VCO tuning varactors on both the integrated-path and feed forward path. | ||

| 0x23 | 0x03 | SYNTH_LPFILT3 | 0x04 | Value of resistor R2 in feed-forward path of loop filter. | ||

| 0x23 | 0x04 | SYNTH_LPFILT2 | 0x0c | Value of capacitor C2 in feed-forward path of loop filter. | ||

| 0x23 | 0x05 | SYNTH_LPFILT1 | 0x73 | Value of capacitors C1 and C3 in feed-forward path of loop filter. | ||

| 0x23 | 0x06 | SYNTH_LPFILT0 | 0x03 | Bias current of the active amplifier in the feed-forward loop filter. | ||

| 0x23 | 0x07 | SYNTH_VCO_KVCAL | 0x05 | Scaling entire KV of VCO. | ||

| FREQ_CONTROL (0x40) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

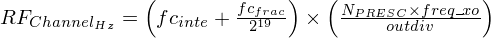

| 0x40 | 0x00 | FREQ_CONTROL_INTE | 0x3c | Frac-N PLL Synthesizer integer divide number. | ||

| 0x40 | 0x01 0x02 0x03 |

FREQ_CONTROL_FRAC | 0x08 0x00 0x00 |

Frac-N PLL fraction number. | ||

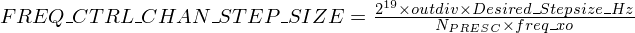

| 0x40 | 0x04 0x05 |

FREQ_CONTROL_CHANNEL_STEP_SIZE | 0x00 0x00 |

EZ Frequency Programming channel step size. | ||

| 0x40 | 0x06 | FREQ_CONTROL_W_SIZE | 0x20 | Set window gating period (in number of crystal reference clock cycles) for counting VCO frequency during calibration. | ||

| PTI (0xf0) | ||||||

|---|---|---|---|---|---|---|

| Group | Number | Name | Default | Summary | Feature Available | |

| 0xf0 | 0x00 | PTI_CTL | 0x80 | Packet Trace Interface control fields. | ||

| 0xf0 | 0x01 0x02 |

PTI_BAUD | 0x13 0x88 |

Desired baud rate for the PTI interface. | ||

| 0xf0 | 0x03 | PTI_LOG_EN | 0x00 | Enables what the PTI logs. | ||

Command Details

COMMON_COMMANDS

NOP

- Number: 0x00

- Summary: No Operation command.

- Purpose:

- This command may be used to ensure that communication with the device has been established. Upon receipt of this command, the chip performs no action except to return CTS.

- Argument Stream:

NOP Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x00 - Reply Stream:

NOP Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS - Argument Fields:

- Reply Fields:

PART_INFO

- Number: 0x01

- Summary: Reports basic information about the device.

- Purpose:

- Returns Part Number, Part Version, ROM ID, etc.

- Argument Stream:

PART_INFO Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x01 - Reply Stream:

PART_INFO Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 CHIPREV CHIPREV 0x02 PART PART[15:8] 0x03 PART[7:0] 0x04 PBUILD PBUILD 0x05 ID ID[15:8] 0x06 ID[7:0] 0x07 CUSTOMER CUSTOMER 0x08 ROMID ROMID - Argument Fields:

- Reply Fields:

- Description:

- Chip Mask Revision.

- Type:

- U8

- Description:

- Part Number (e.g., si4461 will return - 0x4461).

- Type:

- U16

- Description:

- Part Build.

- Type:

- U8

- Description:

- Customer ID.

- Type:

- U8

- Description:

- ROM Id.

- Type:

- U8

FUNC_INFO

- Number: 0x10

- Summary: Returns the Function revision information of the device.

- Purpose:

- Return Function revision numbers for currently loaded functional mode. Contrast with PART_INFO.

- Argument Stream:

FUNC_INFO Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x10 - Reply Stream:

FUNC_INFO Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 REVEXT REVEXT 0x02 REVBRANCH REVBRANCH 0x03 REVINT REVINT 0x04 PATCH PATCH[15:8] 0x05 PATCH[7:0] 0x06 FUNC FUNC - Argument Fields:

- Reply Fields:

- Description:

- External revision number.

- Type:

- U8

- Min:

- 0x0

- Max:

- 0xff

- Description:

- Branch revision number.

- Type:

- U8

- Min:

- 0x0

- Max:

- 0xff

- Description:

- Internal revision number.

- Type:

- U8

- Min:

- 0x0

- Max:

- 0xff

- Description:

- ID of applied patch. This is also the last 2 bytes in the associated patch file (*.csg).

- 0x0000 = No patch applied.

- Type:

- U16

SET_PROPERTY

- Number: 0x11

- Summary: Sets the value of one or more properties.

- Purpose:

- This command sets the value of one or more properties. Properties are similar to parameters passed to an API command, but are not expected to change frequently. They are typically used to configure the operation of various internal circuit blocks.

- Properties may be controlled by higher layers of the user's software. Setting some properties may not cause the device to take immediate action; however, the property will take effect once a command which uses that property is issued.

- Properties that affect similar circuit blocks or functions (e.g., MODEM or PA or SYNTH properties) are grouped together and share the same GROUP parameter value. Each property within that GROUP has a different offset number or index.

- A single property may be configured by setting the NUM_PROPS parameter = 0x01, setting the START_PROP parameter to the offset number of that particular property, followed by a single data byte representing the desired value of the property.

- Multiple contiguous properties may be configured by setting the NUM_PROPS parameter equal to the number of desired properties, setting the START_PROP parameter to the offset number of the first property within that contiguous block of properties, followed by a string of data bytes representing the desired values of the properties.

- The maximum number of properties that may be set with a single SET_PROPERTY command is 12.

- This command sets the value of one or more properties. Properties are similar to parameters passed to an API command, but are not expected to change frequently. They are typically used to configure the operation of various internal circuit blocks.

- Argument Stream:

SET_PROPERTY Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x11 0x01 GROUP GROUP 0x02 NUM_PROPS NUM_PROPS 0x03 START_PROP START_PROP 0x04 DATA[0] DATA ... ... ... 0x0f DATA[11] DATA - Reply Stream:

SET_PROPERTY Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS - Argument Fields:

- Description:

- Selects the property group to be configured.

- Type:

- U8

- Description:

- Selects the number of contiguous properties to be written, starting at START_PROP.

- Type:

- U8

- Min:

- 0x1

- Max:

- 0xc

- Description:

- Selects the offset number or index of the property within the specified group. The available properties are determined by the part number and the POWER_UP:FUNC selection.

- Type:

- U8

- Description:

- Value to be written to the property located at START_PROP + N. this parameter is not relevant if NUM_PROPS < N + 1. (where N is the Data index)

- Type:

- U8

- Reply Fields:

GET_PROPERTY

- Number: 0x12

- Summary: Retrieves the value of one or more properties

- Purpose:

- This command retrieves the value of one or more properties. Properties are similar to parameters passed to an API command, but are not expected to change frequently. They are typically used to configure the operation of various internal circuit blocks. The returned value represents the default property value upon POWER_UP or the value set previously with a SET_PROPERTY command.

- Properties that affect similar circuit blocks or functions (e.g., MODEM or PA or SYNTH properties) are grouped together and share the same GROUP parameter value. Each property within that GROUP has a different offset number or index.

- A single property may be retrieved by setting the NUM_PROPS parameter = 0x01 and setting the START_PROP parameter to the offset number of that particular property. The first data byte of the reply stream represents the value of that property.

- Multiple contiguous properties may be retrieved by setting the NUM_PROPS parameter equal to the number of desired properties and setting the START_PROP parameter to the offset number of the first property within that contiguous block of properties. The data bytes of the reply stream represent the values of the contiguous properties in sequential order of their offset number.

- The maximum number of properties that may be retrieved with a single GET_PROPERTY command is 16.

- This command retrieves the value of one or more properties. Properties are similar to parameters passed to an API command, but are not expected to change frequently. They are typically used to configure the operation of various internal circuit blocks. The returned value represents the default property value upon POWER_UP or the value set previously with a SET_PROPERTY command.

- Argument Stream:

GET_PROPERTY Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x12 0x01 GROUP GROUP 0x02 NUM_PROPS NUM_PROPS 0x03 START_PROP START_PROP - Reply Stream:

GET_PROPERTY Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 DATA[0] DATA ... ... ... 0x10 DATA[15] DATA - Argument Fields:

- Description:

- Selects the property group to be retrieved.

- Type:

- U8

- Description:

- Selects the number of contiguous properties to be retrieved, starting at START_PROP.

- Type:

- U8

- Min:

- 0x1

- Max:

- 0x10

- Description:

- Selects the offset number or index of the property within the specified group. the available properties are determined by the part number and the POWER_UP:FUNC selection

- Type:

- U8

- Reply Fields:

- Description:

- Retrieved value of the properties located starting at START_PROP. Response bytes in this field are not relevant starting at DATA[NUM_PROPS] and contiuing to the end of the DATA response field.

- Type:

- U8

GPIO_PIN_CFG

- Number: 0x13

- Summary: Configures the GPIO pins.

- Purpose:

- The chip provides General Purpose Input/Output (GPIO) pins for handling a variety of signals. This command is used to select the desired signal for each GPIO pin from an enumerated list of available signals.

- The drive strength is selectable for those pins configured as outputs. The selected drive strength is applied simultaneously to all outputs; it is currently not possible to individually configure each GPIO pin for different drive strengths.

- Each pin provides a weak pull-up resistor (~1 Megohm) that may be individually enabled or disabled. It is recommended to disable the pull-up resistor when the pin is configured as an input and driven from an external source (other than an open-drain source).

- The pins referenced by this command share similar hardware characteristics (i.e., drive strength, pull-up resistors, input/output configurability) but may provide access to different sets of signals. Specifically, the NIRQ and SDO pins are not "signal equivalent" to the GPIO pins.

- The chip provides General Purpose Input/Output (GPIO) pins for handling a variety of signals. This command is used to select the desired signal for each GPIO pin from an enumerated list of available signals.

- Argument Stream:

GPIO_PIN_CFG Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x13 0x01 GPIO[0] 0 PULL_CTL GPIO_MODE ... ... ... ... ... 0x04 GPIO[3] 0 PULL_CTL GPIO_MODE 0x05 NIRQ 0 PULL_CTL NIRQ_MODE 0x06 SDO 0 PULL_CTL SDO_MODE 0x07 GEN_CONFIG 0 DRV_STRENGTH 0 0 0 0 0 - Reply Stream:

GPIO_PIN_CFG Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 GPIO[0] GPIO_STATE X GPIO_MODE ... ... ... ... ... 0x04 GPIO[3] GPIO_STATE X GPIO_MODE 0x05 NIRQ NIRQ_STATE X NIRQ_MODE 0x06 SDO SDO_STATE X SDO_MODE 0x07 GEN_CONFIG X DRV_STRENGTH X X X X X - Argument Fields:

- Description:

- The pin pull-up control.

- Format:

- Enumeration

Name Value Description Feature Available PULL_DIS 0 Disable pull-up resistor (recommended setting if the pin is driven from an external source, other than an open-drain source). revB1A PULL_EN 1 Enable pull-up resistor. revB1A

- Description:

- The pin mode.

- Format:

- Enumeration

Name Value Description Feature Available DONOTHING 0 Behavior of this pin is not modified. revB1A TRISTATE 1 Input and output drivers disabled. revB1A DRIVE0 2 Pin is configured as a CMOS output and driven low. revB1A DRIVE1 3 Pin is configured as a CMOS output and driven high. revB1A INPUT 4 Pin is configured as a CMOS input. This is used for all GPIO functions that require the pin to be an input (e.g., TXDATA input for TX Direct Mode). However, configuration of this pin as an input does NOT additionally select which internal circuit receives that input; that functionality is controlled by other properties, as appropriate. revB1A 32K_CLK 5 Outputs 32 kHz clock selected using GLOBAL_CLK_CFG:CLK_32K_SEL. Output low if the 32 kHz clock is not enabled. revB1A BOOT_CLK 6 Outputs the boot clock signal. This signal will only be present when the chip is in the SPI_ACTIVE state as that is the only state in which the boot clock is active. revB1A DIV_CLK 7 Outputs the divided clock signal (or the divided boot clock signal in SPI ACTIVE state). This output is low while the chip is in SLEEP state as the source (e.g., the Xtal Oscillator) for the divided clock signal is not running, and outputs the divided XtalOsc signal in all other states. The divider is configured using the GLOBAL_CLK_CFG:DIVIDED_CLK_SEL. revB1A CTS 8 Clear To Send signal. This output goes high when the command handler is able to receive a new command, and is low otherwise. revB1A INV_CTS 9 Inverted Clear To Send signal. This output goes low when clear to send a new command, and is high otherwise. revB1A CMD_OVERLAP 10 This output is low unless a command overlap occurs (i.e., another command is sent before the command handler completes processing a previous command). When command overlap occurs, this output goes high until the rising edge of CTS. revB1A SDO 11 Outputs the Serial Data Out (SDO) signal for the SPI bus. revB1A POR 12 This output goes low during Power-On Reset and goes high upon completion of POR. revB1A CAL_WUT 13 This output is normally low, and pulses high for one cycle of the 32 kHz clock upon expiration of the Calibration Timer. The 32 kHz clock must be enabled in order to use the Calibration Timer. The Calibration Timer period is configured using GLOBAL_WUT_CONFIG:WUT_CAL_PERIOD and enabled by GLOBAL_WUT_CONFIG:CAL_EN. revB1A WUT 14 This output is normally low, and pulses high for 2(WUT_R+1) cycles of the 32 kHz clock upon expiration of the Wake-Up Timer (WUT). The 32 kHz clock must be enabled in order to use the WUT. The period of the WUT is configured using GLOBAL_WUT_M, and GLOBAL_WUT_R and enabled by GLOBAL_WUT_CONFIG:WUT_EN. revB1A EN_PA 15 This output goes high when the internal PA is enabled. revB1A TX_DATA_CLK 16 Outputs the TX Data Clock signal. This signal is a square wave at the selected TX data rate, and is intended for use in TX Direct Synchronous Mode (i.e., in conjunction with a pin configured for TX Data Input). revB1A TX_DATA 19 Outputs the TX data bits pulled from the TX FIFO and sent to the TX modulator. This is an output signal (primarily for diagnostic purposes) and is NOT used as an input for TX Direct Sync/Async mode. revB1A IN_SLEEP 28 This output goes high when the chip is NOT in SLEEP state, and goes low when in SLEEP state. revB1A PKT_TRACE 29 Outputs packet trace data when not in sleep state. Output low when in sleep state. TX_STATE 32 This output is set high while in TX state and is low otherwise. The TX_STATE and RX_STATE signals are typically used for control of peripheral circuits (e.g., a T/R Switch). revB1A TX_FIFO_EMPTY 35 This output is high while the number of bytes of empty space in the TX FIFO exceeds the threshold value set by the PKT_TX_THRESHOLD property, and is low otherwise. revB1A LOW_BATT 36 This output is high while the battery voltage drops below the threshold value set by the GLOBAL_LOW_BATT_THRESH property, and is low otherwise.

- Description:

- The pin pull-up control.

- Format:

- Enumeration

Name Value Description Feature Available PULL_DIS 0 Disable pull-up resistor (recommended setting if the pin is driven from an external source, other than an open-drain source). revB1A PULL_EN 1 Enable pull-up resistor. revB1A

- Description:

- The pin mode.

- Format:

- Enumeration

Name Value Description Feature Available DONOTHING 0 Behavior of this pin is not modified. revB1A TRISTATE 1 Input and output drivers disabled. revB1A DRIVE0 2 Pin is configured as a CMOS output and driven low. revB1A DRIVE1 3 Pin is configured as a CMOS output and driven high. revB1A INPUT 4 Pin is configured as a CMOS input. This is used for all GPIO functions that require the pin to be an input (e.g., TXDATA input for TX Direct Mode). However, configuration of this pin as an input does NOT additionally select which internal circuit receives that input; that functionality is controlled by other properties, as appropriate. revB1A DIV_CLK 7 Outputs the divided clock signal (or the divided boot clock signal in SPI ACTIVE state). This output is low while the chip is in SLEEP state as the source (e.g., the Xtal Oscillator) for the divided clock signal is not running, and outputs the divided XtalOsc signal in all other states. The divider is configured using the GLOBAL_CLK_CFG:DIVIDED_CLK_SEL. revB1A CTS 8 Clear To Send signal. This output goes high when the command handler is able to receive a new command, and is low otherwise. revB1A SDO 11 Outputs the Serial Data Out (SDO) signal for the SPI bus. revB1A POR 12 This output goes low during Power-On Reset and goes high upon completion of POR. revB1A EN_PA 15 This output goes high when the internal PA is enabled. revB1A TX_DATA_CLK 16 Outputs the TX Data Clock signal. This signal is a square wave at the selected TX data rate, and is intended for use in TX Direct Synchronous Mode (i.e., in conjunction with a pin configured for TX Data Input). revB1A TX_DATA 19 Outputs the TX data bits pulled from the TX FIFO and sent to the TX modulator. This is an output signal (primarily for diagnostic purposes) and is NOT used as an input for TX Direct Sync/Async mode. revB1A PKT_TRACE 29 Outputs packet trace data when not in sleep state. Output low when in sleep state. NIRQ 39 Active low interrupt signal. revBlA

- Description:

- The pin pull-up control.

- Format:

- Enumeration

Name Value Description Feature Available PULL_DIS 0 Disable pull-up resistor (recommended setting if the pin is driven from an external source, other than an open-drain source). revB1A PULL_EN 1 Enable pull-up resistor. revB1A

- Description:

- The pin mode.

- Format:

- Enumeration

Name Value Description Feature Available DONOTHING 0 Behavior of this pin is not modified. revB1A TRISTATE 1 Input and output drivers disabled. revB1A DRIVE0 2 Pin is configured as a CMOS output and driven low. revB1A DRIVE1 3 Pin is configured as a CMOS output and driven high. revB1A INPUT 4 Pin is configured as a CMOS input. This is used for all GPIO functions that require the pin to be an input (e.g., TXDATA input for TX Direct Mode). However, configuration of this pin as an input does NOT additionally select which internal circuit receives that input; that functionality is controlled by other properties, as appropriate. revB1A 32K_CLK 5 Outputs 32 kHz clock selected using GLOBAL_CLK_CFG:CLK_32K_SEL. Output low if the 32 kHz clock is not enabled. revB1A DIV_CLK 7 Outputs the divided clock signal (or the divided boot clock signal in SPI ACTIVE state). This output is low while the chip is in SLEEP state as the source (e.g., the Xtal Oscillator) for the divided clock signal is not running, and outputs the divided XtalOsc signal in all other states. The divider is configured using the GLOBAL_CLK_CFG:DIVIDED_CLK_SEL. revB1A CTS 8 Clear To Send signal. This output goes high when the command handler is able to receive a new command, and is low otherwise. revB1A SDO 11 Outputs the Serial Data Out (SDO) signal for the SPI bus. revB1A POR 12 This output goes low during Power-On Reset and goes high upon completion of POR. revB1A WUT 14 This output is normally low, and pulses high for 2(WUT_R+1) cycles of the 32 kHz clock upon expiration of the Wake-Up Timer (WUT). The 32 kHz clock must be enabled in order to use the WUT. The period of the WUT is configured using GLOBAL_WUT_M, and GLOBAL_WUT_R and enabled by GLOBAL_WUT_CONFIG:WUT_EN. revB1A EN_PA 15 This output goes high when the internal PA is enabled. revB1A TX_DATA_CLK 16 Outputs the TX Data Clock signal. This signal is a square wave at the selected TX data rate, and is intended for use in TX Direct Synchronous Mode (i.e., in conjunction with a pin configured for TX Data Input). revB1A TX_DATA 19 Outputs the TX data bits pulled from the TX FIFO and sent to the TX modulator. This is an output signal (primarily for diagnostic purposes) and is NOT used as an input for TX Direct Sync/Async mode. revB1A

- Description:

- Selects the level of drive strength for those GPIO/NIRQ/SDO pins configured as outputs.

- The selected level of drive strength is applied simultaneously to all output pins, with the following exception: GPIO0 will exhibit a weaker drive strength than the other GPIO pins but only in the lowest drive strength setting; its drive strength is the same for all other settings.

- Selects the level of drive strength for those GPIO/NIRQ/SDO pins configured as outputs.

- Format:

- Enumeration

Name Value Description Feature Available HIGH 0 GPIOs configured as outputs will have the highest drive strength. revB1A MED_HIGH 1 GPIOs configured as outputs will have a medium drive strength. revB1A MED_LOW 2 GPIOs configured as outputs will have a medium drive strength. revB1A LOW 3 GPIOs configured as outputs will have the lowest drive strength. revB1A

- Reply Fields:

- Description:

- Reads back the logic level on the pin.

- Format:

- Enumeration

Name Value Description Feature Available INACTIVE 0 Pin was read back as a 0. revB1A ACTIVE 1 Pin was read back as a 1. revB1A

- Description:

- Reads back the enumeration of the currently selected function for the pin.

- Format:

- Enumeration

Name Value Description Feature Available DONOTHING 0 Behavior of this pin is not modified. revB1A TRISTATE 1 Input and output drivers disabled. revB1A DRIVE0 2 Pin is configured as a CMOS output and driven low. revB1A DRIVE1 3 Pin is configured as a CMOS output and driven high. revB1A INPUT 4 Pin is configured as a CMOS input. This is used for all GPIO functions that require the pin to be an input (e.g., TXDATA input for TX Direct Mode). However, configuration of this pin as an input does NOT additionally select which internal circuit receives that input; that functionality is controlled by other properties, as appropriate. revB1A 32K_CLK 5 Outputs 32 kHz clock selected using GLOBAL_CLK_CFG:CLK_32K_SEL. Output low if the 32 kHz clock is not enabled. revB1A BOOT_CLK 6 Outputs the boot clock signal. This signal will only be present when the chip is in the SPI_ACTIVE state as that is the only state in which the boot clock is active. revB1A DIV_CLK 7 Outputs the divided clock signal (or the divided boot clock signal in SPI ACTIVE state). This output is low while the chip is in SLEEP state as the source (e.g., the Xtal Oscillator) for the divided clock signal is not running, and outputs the divided XtalOsc signal in all other states. The divider is configured using the GLOBAL_CLK_CFG:DIVIDED_CLK_SEL. revB1A CTS 8 Clear To Send signal. This output goes high when the command handler is able to receive a new command, and is low otherwise. revB1A INV_CTS 9 Inverted Clear To Send signal. This output goes low when clear to send a new command, and is high otherwise. revB1A CMD_OVERLAP 10 This output is low unless a command overlap occurs (i.e., another command is sent before the command handler completes processing a previous command). When command overlap occurs, this output goes high until the rising edge of CTS. revB1A SDO 11 Outputs the Serial Data Out (SDO) signal for the SPI bus. revB1A POR 12 This output goes low during Power-On Reset and goes high upon completion of POR. revB1A CAL_WUT 13 This output is normally low, and pulses high for one cycle of the 32 kHz clock upon expiration of the Calibration Timer. The 32 kHz clock must be enabled in order to use the Calibration Timer. The Calibration Timer period is configured using GLOBAL_WUT_CONFIG:WUT_CAL_PERIOD and enabled by GLOBAL_WUT_CONFIG:CAL_EN. revB1A WUT 14 This output is normally low, and pulses high for 2(WUT_R+1) cycles of the 32 kHz clock upon expiration of the Wake-Up Timer (WUT). The 32 kHz clock must be enabled in order to use the WUT. The period of the WUT is configured using GLOBAL_WUT_M, and GLOBAL_WUT_R and enabled by GLOBAL_WUT_CONFIG:WUT_EN. revB1A EN_PA 15 This output goes high when the internal PA is enabled. revB1A TX_DATA_CLK 16 Outputs the TX Data Clock signal. This signal is a square wave at the selected TX data rate, and is intended for use in TX Direct Synchronous Mode (i.e., in conjunction with a pin configured for TX Data Input). revB1A TX_DATA 19 Outputs the TX data bits pulled from the TX FIFO and sent to the TX modulator. This is an output signal (primarily for diagnostic purposes) and is NOT used as an input for TX Direct Sync/Async mode. revB1A IN_SLEEP 28 This output goes high when the chip is NOT in SLEEP state, and goes low when in SLEEP state. revB1A PKT_TRACE 29 Outputs packet trace data when not in sleep state. Output low when in sleep state. TX_STATE 32 This output is set high while in TX state and is low otherwise. The TX_STATE and RX_STATE signals are typically used for control of peripheral circuits (e.g., a T/R Switch). revB1A TX_FIFO_EMPTY 35 This output is high while the number of bytes of empty space in the TX FIFO exceeds the threshold value set by the PKT_TX_THRESHOLD property, and is low otherwise. revB1A LOW_BATT 36 This output is high while the battery voltage drops below the threshold value set by the GLOBAL_LOW_BATT_THRESH property, and is low otherwise.

- Description:

- Reads back the logic level on the NIRQ pin.

- Format:

- Enumeration

Name Value Description Feature Available INACTIVE 0 Pin was read back as a 0. revB1A ACTIVE 1 Pin was read back as a 1. revB1A

- Description:

- Reads back the enumeration of the currently selected function for the NIRQ pin.

- Format:

- Enumeration

Name Value Description Feature Available DONOTHING 0 Behavior of this pin is not modified. revB1A TRISTATE 1 Input and output drivers disabled. revB1A DRIVE0 2 Pin is configured as a CMOS output and driven low. revB1A DRIVE1 3 Pin is configured as a CMOS output and driven high. revB1A INPUT 4 Pin is configured as a CMOS input. This is used for all GPIO functions that require the pin to be an input (e.g., TXDATA input for TX Direct Mode). However, configuration of this pin as an input does NOT additionally select which internal circuit receives that input; that functionality is controlled by other properties, as appropriate. revB1A DIV_CLK 7 Outputs the divided clock signal (or the divided boot clock signal in SPI ACTIVE state). This output is low while the chip is in SLEEP state as the source (e.g., the Xtal Oscillator) for the divided clock signal is not running, and outputs the divided XtalOsc signal in all other states. The divider is configured using the GLOBAL_CLK_CFG:DIVIDED_CLK_SEL. revB1A CTS 8 Clear To Send signal. This output goes high when the command handler is able to receive a new command, and is low otherwise. revB1A SDO 11 Outputs the Serial Data Out (SDO) signal for the SPI bus. revB1A POR 12 This output goes low during Power-On Reset and goes high upon completion of POR. revB1A EN_PA 15 This output goes high when the internal PA is enabled. revB1A TX_DATA_CLK 16 Outputs the TX Data Clock signal. This signal is a square wave at the selected TX data rate, and is intended for use in TX Direct Synchronous Mode (i.e., in conjunction with a pin configured for TX Data Input). revB1A TX_DATA 19 Outputs the TX data bits pulled from the TX FIFO and sent to the TX modulator. This is an output signal (primarily for diagnostic purposes) and is NOT used as an input for TX Direct Sync/Async mode. revB1A PKT_TRACE 29 Outputs packet trace data when not in sleep state. Output low when in sleep state. NIRQ 39 Active low interrupt signal. revBlA

- Description:

- Reads back the logic level on the SDO pin.

- Format:

- Enumeration

Name Value Description Feature Available INACTIVE 0 Pin was read back as a 0. revB1A ACTIVE 1 Pin was read back as a 1. revB1A

- Description:

- Reads back the enumeration of the currently selected function for the SDO pin.

- Format:

- Enumeration

Name Value Description Feature Available DONOTHING 0 Behavior of this pin is not modified. revB1A TRISTATE 1 Input and output drivers disabled. revB1A DRIVE0 2 Pin is configured as a CMOS output and driven low. revB1A DRIVE1 3 Pin is configured as a CMOS output and driven high. revB1A INPUT 4 Pin is configured as a CMOS input. This is used for all GPIO functions that require the pin to be an input (e.g., TXDATA input for TX Direct Mode). However, configuration of this pin as an input does NOT additionally select which internal circuit receives that input; that functionality is controlled by other properties, as appropriate. revB1A 32K_CLK 5 Outputs 32 kHz clock selected using GLOBAL_CLK_CFG:CLK_32K_SEL. Output low if the 32 kHz clock is not enabled. revB1A DIV_CLK 7 Outputs the divided clock signal (or the divided boot clock signal in SPI ACTIVE state). This output is low while the chip is in SLEEP state as the source (e.g., the Xtal Oscillator) for the divided clock signal is not running, and outputs the divided XtalOsc signal in all other states. The divider is configured using the GLOBAL_CLK_CFG:DIVIDED_CLK_SEL. revB1A CTS 8 Clear To Send signal. This output goes high when the command handler is able to receive a new command, and is low otherwise. revB1A SDO 11 Outputs the Serial Data Out (SDO) signal for the SPI bus. revB1A POR 12 This output goes low during Power-On Reset and goes high upon completion of POR. revB1A WUT 14 This output is normally low, and pulses high for 2(WUT_R+1) cycles of the 32 kHz clock upon expiration of the Wake-Up Timer (WUT). The 32 kHz clock must be enabled in order to use the WUT. The period of the WUT is configured using GLOBAL_WUT_M, and GLOBAL_WUT_R and enabled by GLOBAL_WUT_CONFIG:WUT_EN. revB1A EN_PA 15 This output goes high when the internal PA is enabled. revB1A TX_DATA_CLK 16 Outputs the TX Data Clock signal. This signal is a square wave at the selected TX data rate, and is intended for use in TX Direct Synchronous Mode (i.e., in conjunction with a pin configured for TX Data Input). revB1A TX_DATA 19 Outputs the TX data bits pulled from the TX FIFO and sent to the TX modulator. This is an output signal (primarily for diagnostic purposes) and is NOT used as an input for TX Direct Sync/Async mode. revB1A

- Description:

- Reads back the enumeration of the currently selected drive strength.

- Format:

- Enumeration

Name Value Description Feature Available HIGH 0 GPIOs configured as outputs will have the highest drive strength. revB1A MED_HIGH 1 GPIOs configured as outputs will have a medium drive strength. revB1A MED_LOW 2 GPIOs configured as outputs will have a medium drive strength. revB1A LOW 3 GPIOs configured as outputs will have the lowest drive strength. revB1A

FIFO_INFO

- Number: 0x15

- Summary: Access the current byte counts in the TX and RX FIFOs, and provide for resetting the FIFOs.

- Purpose:

- The chip provides for two separate 64-byte FIFO memories for the purpose of storing transmit and receive data. (When the GLOBAL_CONFIG:FIFO_MODE bit is set, these two FIFOs are combined into a single 129-byte shared FIFO.)

- The reply stream for this command returns the current number of received bytes stored in the RX FIFO, and the number of remaining empty bytes in the TX FIFO.

- The command may also be used to reset the individual FIFOs. This is typically used for error recovery (e.g., after encountering a CRC error in RX mode). Any valid data that has not yet been retrieved from the RX FIFO will be lost as a result of a reset; it is recommended to read such data prior to a reset. The FIFOs do not need to be reset prior to initial use after power-up.

- The FIFO reset function (if enabled) is processed prior to returning the byte count in the FIFOs. Thus the reply stream to a FIFO_INFO command that resets the FIFOs will return byte counts that indicate the FIFOs are empty.

- A FIFO reset command should not be sent while actively receiving or transmitting a packet, as this may corrupt the index pointers into the FIFOs and result in loss of stored information.

- The FIFO:TX and FIFO:RX bits are self-clearing; that is, there is no need to send the command twice (e.g., with the reset bits set the first time, and cleared the second time).

- Argument Stream:

FIFO_INFO Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x15 0x01 FIFO 0 0 0 0 0 0 0 TX - Reply Stream:

FIFO_INFO Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 RESERVED0 X X X X X X X X 0x02 TX_FIFO_SPACE TX_FIFO_SPACE - Argument Fields:

- Description:

- Resets the TX FIFO.

- The TX FIFO mode specified in property GLOBAL_CONFIG:FIFO_MODE will be effective after reset.

- Resets the TX FIFO.

- Format:

- Enumeration

Name Value Description Feature Available FALSE 0 Do not reset the TX data FIFO. revB1A TRUE 1 Reset the TX data FIFO. revB1A

- Reply Fields:

- Description:

- Returns the number of empty bytes (i.e., space) currently available in the TX FIFO.

- Type:

- U8

GET_INT_STATUS

- Number: 0x20

- Summary: Returns the interrupt status of ALL the possible interrupt events (both STATUS and PENDING). Optionally, it may be used to clear latched (PENDING) interrupt events.

- Purpose:

- Returns the current interrupt status of ALL the possible interrupt events (both STATUS and PENDING) and optionally clears PENDING interrupts.

- STATUS indicates the current state of an internal interrupt event such as preamble/sync word detection, packet sent/received, etc. For example, PREAMBLE_DETECT is low before detection of a valid preamble, but goes high when the preamble arrives and is successfully detected. STATUS is cleared automatically upon termination or cessation of the corresponding internal interrupt event.

- PENDING simply latches the rising edge of the corresponding STATUS, and does not change until cleared by a GET_INT_STATUS command (or GET_CHIP_STATUS, GET_PH_STATUS, GET_MODEM_STATUS). For example, PREAMBLE_DETECT_PEND is low before detection of a valid preamble, goes high with PREAMBLE_DETECT, and remains high until cleared.

- It is possible to poll for interrupts by reading the STATUS and PENDING response bytes, as they are always up-to-date. Additionally, PENDING interrupts may generate a HW interrupt on the NIRQ output pin, if the interrupt is enabled via INT_CTL_ENABLE, INT_CTL_PH_ENABLE, INT_CTL_MODEM_ENABLE, and INT_CTL_CHIP_ENABLE properties.

- Sending the GET_INT_STATUS command with NO input parameters results in clearing all of the PENDING interrupts.

- When PENDING interrupts are being cleared, the reply stream reflects their status prior to clearing.

- Argument Stream:

GET_INT_STATUS Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x20 0x01 PH_CLR_PEND 0 0 PACKET_SENT_PEND_CLR 0 0 0 TX_FIFO_ALMOST_EMPTY_PEND_CLR 0 0x02 RESERVED0 0 0 0 0 0 0 0 0 0x03 CHIP_CLR_PEND 0 CAL_PEND_CLR FIFO_UNDERFLOW_OVERFLOW_ERROR_PEND_CLR STATE_CHANGE_PEND_CLR CMD_ERROR_PEND_CLR CHIP_READY_PEND_CLR LOW_BATT_PEND_CLR WUT_PEND_CLR - Reply Stream:

GET_INT_STATUS Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 INT_PEND X X X X X CHIP_INT_PEND MODEM_INT_PEND PH_INT_PEND 0x02 INT_STATUS X X X X X CHIP_INT_STATUS MODEM_INT_STATUS PH_INT_STATUS 0x03 PH_PEND X X PACKET_SENT_PEND X X X TX_FIFO_ALMOST_EMPTY_PEND X 0x04 PH_STATUS X X PACKET_SENT X X X TX_FIFO_ALMOST_EMPTY X 0x05 RESERVED0 X X X X X X X X 0x06 RESERVED1 X X X X X X X X 0x07 CHIP_PEND X CAL_PEND FIFO_UNDERFLOW_OVERFLOW_ERROR_PEND STATE_CHANGE_PEND CMD_ERROR_PEND CHIP_READY_PEND LOW_BATT_PEND WUT_PEND 0x08 CHIP_STATUS X CAL FIFO_UNDERFLOW_OVERFLOW_ERROR STATE_CHANGE CMD_ERROR CHIP_READY LOW_BATT WUT - Argument Fields:

- Description:

- If clear, clear any pending PACKET_SENT interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending TX_FIFO_ALMOST_EMPTY interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending CAL interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending FIFO_UNDERFLOW_OVERFLOW_ERROR interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending STATE_CHANGE interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending CMD_ERROR interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending CHIP_READY interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending LOW_BATT interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Description:

- If clear, clear any pending WUT interrupt. If set, leave interrupt pending.

- Type:

- BOOL

- Reply Fields:

- Description:

- If set, an enabled CHIP_PEND bit is set indicating an interrupt is pending. See the GET_INT_STATUS:CHIP_STATUS field for the triggering events within the Chip Status Interrupt group.

- Type:

- BOOL

- Description:

- If set, an enabled MODEM_PEND bit is set indicating an interrupt is pending. See the GET_INT_STATUS:MODEM_STATUS field for the triggering events within the Modem Interrupt group.

- Type:

- BOOL

- Description:

- If set, an enabled PH_PEND bit is set indicating an interrupt is pending. See the GET_INT_STATUS:PH_STATUS field for the triggering events within the Packet Handler Interrupt group.

- Type:

- BOOL

- Description:

- If set, the Chip Status Interrupt group has an interrupt pending. See the GET_INT_STATUS:CHIP_STATUS field for the triggering events within the Chip Status Interrupt group.

- Type:

- BOOL

- Description:

- If set, the Modem Interrupt group has an interrupt pending. See the GET_INT_STATUS:MODEM_STATUS field for the triggering events within the Modem Interrupt group.

- Type:

- BOOL

- Description:

- If set, the Packet Handler Interrupt group has an interrupt pending. See the GET_INT_STATUS:PH_STATUS field for the triggering events within the Packet Handler Interrupt group.

- Type:

- BOOL

- Description:

- If set, a rising edge of the PACKET_SENT status bit has been detected and therefore a PACKET_SENT interrupt is pending. See associated PACKET_SENT status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the TX_FIFO_ALMOST_EMPTY status bit has been detected and therefore a TX_FIFO_ALMOST_EMPTY interrupt is pending. See associated TX_FIFO_ALMOST_EMPTY status bit for more details.

- Type:

- BOOL

- Description:

- Set to indicate that data bytes in the TX FIFO were transmitted successfully. Cleared upon entry into TX state.

- Type:

- BOOL

- Description:

- Set to indicate that the amount of space in the TX FIFO is equal to or greater than the PKT_TX_THRESHOLD value. This interrupt may be used to signal the host MCU to store more data bytes into the TX FIFO, thus providing a means for handling packets with lengths greater than the size of the TX FIFO (i.e., 64 bytes, or 129 bytes in shared FIFO mode). Cleared if the amount of space in the TX FIFO is more than the PKT_TX_THRESHOLD value.

- Type:

- BOOL

- Description:

- If set, a rising edge of the CAL status bit has been detected and therefore a CAL interrupt is pending. See associated CAL status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the FIFO_UNDERFLOW_OVERFLOW_ERROR status bit has been detected and therefore a FIFO_UNDERFLOW_OVERFLOW_ERROR interrupt is pending. See associated FIFO_UNDERFLOW_OVERFLOW_ERROR status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the STATE_CHANGE status bit has been detected and therefore a STATE_CHANGE interrupt is pending. See associated STATE_CHANGE status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the CMD_ERROR status bit has been detected and therefore a CMD_ERROR interrupt is pending. See associated CMD_ERROR status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the CHIP_READY status bit has been detected and therefore a CHIP_READY interrupt is pending. See associated CHIP_READY status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the LOW_BATT status bit has been detected and therefore a LOW_BATT interrupt is pending. See associated LOW_BATT status bit for more details.

- Type:

- BOOL

- Description:

- If set, a rising edge of the WUT status bit has been detected and therefore a WUT interrupt is pending. See associated WUT status bit for more details.

- Type:

- BOOL

- Description:

- Self clearing signal that pulses high to indicate a RC32K calibration event is pending. If this occurs, the RC32K oscillator will be calibrated on the next transition to Sleep/Standby state.

- Type:

- BOOL

- Description:

- Set to indicate that the number of received or transmitted bytes exceeds the size of the RX or TX FIFO, respectively (i.e., 64 bytes for each FIFO, or 129 bytes when sharing the FIFO). Upon such an underflow/overflow event, the FIFO(s) will need to be reset. Cleared by issuing a FIFO_INFO command to reset the FIFOs.

- Type:

- BOOL

- Description:

- Set to indicate a successful transition from one state to another operating state. Cleared when a state transition is in progress.

- Type:

- BOOL

- Description:

- Self clearing signal that pulses high to indicate an error has occurred in the processing of a command. For example, an incorrect command/property ID is sent, or an attempt was made to write a property that is outside of the given property group.

- Type:

- BOOL

- Description:

- Set to indicate the chip (upon completion of the POWER_UP sequence) has reached the state where it is ready to accept commands, or when the IR calibration process is completed. Cleared when the chip is shutdown or when IR calibration has begun.

- Type:

- BOOL

- Description:

- Set to indicate the battery voltage is below the threshold set by GLOBAL_LOW_BATT_THRESH. Cleared to indicate the battery voltage is above the threshold set by GLOBAL_LOW_BATT_THRESH.

- Type:

- BOOL

- Description:

- Self clearing signal that pulses high to indicate the WUT (Wake-up timer) has expired.

- Type:

- BOOL

REQUEST_DEVICE_STATE

- Number: 0x33

- Summary: Request current device state and channel.

- Purpose:

- This command returns information regarding the current operating state and tuned frequency channel of the device.

- Returning the current channel number is often useful in automatic frequency hopping applications, to determine the frequency on which the device found a valid signal.

- It is not possible for this command to return a device state value indicating the chip is in SLEEP or STANDBY mode, as the very act of sending an SPI command while the chip is in SLEEP or STANDBY mode assures that it wakes into SPI_ACTIVE mode.

- This command returns information regarding the current operating state and tuned frequency channel of the device.

- Argument Stream:

REQUEST_DEVICE_STATE Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x33 - Reply Stream:

REQUEST_DEVICE_STATE Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 CURR_STATE X X X X MAIN_STATE 0x02 CURRENT_CHANNEL CURRENT_CHANNEL - Argument Fields:

- Reply Fields:

- Description:

- Returns the current operating state of the device. Please refer to the published datasheet for more details regarding these operational modes.

- Format:

- Enumeration

Name Value Description Feature Available SLEEP 1 (Not Applicable) revB1A SPI_ACTIVE 2 SPI_ACTIVE state. revB1A READY 3 READY state. revB1A READY2 4 Another enumeration for READY state. revB1A TX_TUNE 5 TX_TUNE state. revB1A TX 7 TX state. revB1A

- Description:

- Returns the current tuned channel.

- Type:

- U8

CHANGE_STATE

- Number: 0x34

- Summary: Manually switch the chip to a desired operating state.

- Purpose:

- The chip normally manages the required steps in transitioning between operating states automatically. For example, transmission of a packet may require: waking the chip from SLEEP mode, enabling the Xtal Oscillator (READY mode), calibrating the VCO and tuning the PLL Synthesizer (TX_TUNE mode), enabling the PA and transmission of the packet (TX mode), and returning to an IDLE state. This sequencing is normally handled by the internal state machine.

- This command provides for manually switching to a desired operating state.

- This command may be used to enter TX or RX mode, if desired. However, those modes of operation typically require specification of additional parameters (e.g., channel number, number of packet bytes, etc.) prior to switching mode. For this reason, separate START_TX and START_RX commands are provided that essentially accomplish the CHANGE_STATE = TX or RX functionality, while simultaneously passing the required parameter bytes.

- The chip normally manages the required steps in transitioning between operating states automatically. For example, transmission of a packet may require: waking the chip from SLEEP mode, enabling the Xtal Oscillator (READY mode), calibrating the VCO and tuning the PLL Synthesizer (TX_TUNE mode), enabling the PA and transmission of the packet (TX mode), and returning to an IDLE state. This sequencing is normally handled by the internal state machine.

- Argument Stream:

CHANGE_STATE Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x34 0x01 NEXT_STATE1 0 0 0 0 NEW_STATE - Reply Stream:

CHANGE_STATE Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS - Argument Fields:

- Description:

- Operating state to switch to immediately. Please refer to the published datasheet for more details regarding these operational modes.

- Format:

- Enumeration

Name Value Description Feature Available NOCHANGE 0 No change, remain in current state. revB1A SLEEP 1 SLEEP or STANDBY state, according to the mode of operation of the 32K R-C Osc selected by GLOBAL_CLK_CFG:CLK_32K_SEL. revB1A SPI_ACTIVE 2 SPI_ACTIVE state. revB1A READY 3 READY state. revB1A TX_TUNE 5 TX_TUNE state. revB1A TX 7 TX state. revB1A

- Reply Fields:

READ_CMD_BUFF

- Number: 0x44

- Summary: Used to read CTS and the command response.

- Purpose:

- Processing of API commands is handled by the command handler in the chip. A subsequent command may not be sent until the chip has completed processing of the first command. The chip indicates the ability to receive another command and the availability of response data by issuing a Clear To Send (CTS) signal; it is necessary for the host MCU to poll the chip for this CTS signal. The CTS signal may be polled via SPI command, or monitored on a GPIO line or as an interrupt on the nIRQ pin.

- This command is used to poll the CTS signal via the SPI bus. The NSEL line should be pulled low, followed by sending the READ_CMD_BUFF command on SDI. While NSEL remains asserted low, an additional eight clock pulses are sent on SCLK and the CTS response byte is read on SDO. If the CTS response byte is not 0xFF, the host MCU should pull NSEL high and repeat the polling procedure.

- If the CTS response byte is 0xFF, the host MCU should keep NSEL asserted low and provide additional clock cycles on SCLK to read out as many response bytes (on SDO) as necessary. The host MCU should pull NSEL high upon completion of reading the response stream.

- A primary function of this command is to determine when CTS goes high, and thus by definition this command may be sent while CTS is low. This command itself does not cause CTS to go low.

- Attempting to read response bytes from the command buffer while CTS is not 0xFF will return invalid results. The response bytes are valid only if CTS = 0xFF.

- Processing of API commands is handled by the command handler in the chip. A subsequent command may not be sent until the chip has completed processing of the first command. The chip indicates the ability to receive another command and the availability of response data by issuing a Clear To Send (CTS) signal; it is necessary for the host MCU to poll the chip for this CTS signal. The CTS signal may be polled via SPI command, or monitored on a GPIO line or as an interrupt on the nIRQ pin.

- Argument Stream:

READ_CMD_BUFF Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x44 - Reply Stream:

READ_CMD_BUFF Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS 0x01 BYTE[0] CMD_BUFF ... ... ... 0x10 BYTE[15] CMD_BUFF - Argument Fields:

- Reply Fields:

- Description:

- Byte 0-15 of the command response buffer.

- Type:

- U8

FRR_A_READ

- Number: 0x50

- Summary: Reads the fast response registers (FRR) starting with FRR_A.

- Purpose:

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- The FRR registers may be read in a burst fashion through the FRR_X_READ commands. After the initial 16 clock cycles, each additional eight clock cycles will clock out the contents of the next fast response register in a circular fashion. Example: If the FRR_A_READ command is issued, the registers will be read in the order A-B-C-D, while if the FRR_B_READ command is issued, the registers will be read in the order B-C-D-A, etc.

- This command does not cause CTS to go low, and can be sent and the reply read while CTS is low. The command ID should be clocked in on SDI then the reply should be clocked out on SDO without deasserting NSEL.

- The FRR_CTL_X_MODE properties are used to select the specific parameter values that will be returned by the FRR_X_READ commands. Please refer to the text description for FRR_CTL_X_MODE for more details regarding selection of the parameter(s) held within the FRR registers.

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- Argument Stream:

FRR_A_READ Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x50 - Reply Stream:

FRR_A_READ Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 FRR_A_VALUE FRR_A_VALUE 0x01 FRR_B_VALUE FRR_B_VALUE 0x02 FRR_C_VALUE FRR_C_VALUE 0x03 FRR_D_VALUE FRR_D_VALUE - Argument Fields:

- Reply Fields:

- Description:

- Value in Fast Response Register A.

- Type:

- U8

- Description:

- Value in Fast Response Register B.

- Type:

- U8

- Description:

- Value in Fast Response Register C.

- Type:

- U8

- Description:

- Value in Fast Response Register D.

- Type:

- U8

FRR_B_READ

- Number: 0x51

- Summary: Reads the fast response registers (FRR) starting with FRR_B.

- Purpose:

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- The FRR registers may be read in a burst fashion through the FRR_X_READ commands. After the initial 16 clock cycles, each additional eight clock cycles will clock out the contents of the next fast response register in a circular fashion. Example: If the FRR_A_READ command is issued, the registers will be read in the order A-B-C-D, while if the FRR_B_READ command is issued, the registers will be read in the order B-C-D-A, etc.

- This command does not cause CTS to go low, and can be sent and the reply read while CTS is low. The command ID should be clocked in on SDI then the reply should be clocked out on SDO without deasserting NSEL.

- The FRR_CTL_X_MODE properties are used to select the specific parameter values that will be returned by the FRR_X_READ commands. Please refer to the text description for FRR_CTL_X_MODE for more details regarding selection of the parameter(s) held within the FRR registers.

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- Argument Stream:

FRR_B_READ Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x51 - Reply Stream:

FRR_B_READ Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 FRR_B_VALUE FRR_B_VALUE 0x01 FRR_C_VALUE FRR_C_VALUE 0x02 FRR_D_VALUE FRR_D_VALUE 0x03 FRR_A_VALUE FRR_A_VALUE - Argument Fields:

- Reply Fields:

- Description:

- Value in Fast Response Register B.

- Type:

- U8

- Description:

- Value in Fast Response Register C.

- Type:

- U8

- Description:

- Value in Fast Response Register D.

- Type:

- U8

- Description:

- Value in Fast Response Register A.

- Type:

- U8

FRR_C_READ

- Number: 0x53

- Summary: Reads the fast response registers (FRR) starting with FRR_C.

- Purpose:

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- The FRR registers may be read in a burst fashion through the FRR_X_READ commands. After the initial 16 clock cycles, each additional eight clock cycles will clock out the contents of the next fast response register in a circular fashion. Example: If the FRR_A_READ command is issued, the registers will be read in the order A-B-C-D, while if the FRR_B_READ command is issued, the registers will be read in the order B-C-D-A, etc.

- This command does not cause CTS to go low, and can be sent and the reply read while CTS is low. The command ID should be clocked in on SDI then the reply should be clocked out on SDO without deasserting NSEL.

- The FRR_CTL_X_MODE properties are used to select the specific parameter values that will be returned by the FRR_X_READ commands. Please refer to the text description for FRR_CTL_X_MODE for more details regarding selection of the parameter(s) held within the FRR registers.

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- Argument Stream:

FRR_C_READ Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x53 - Reply Stream:

FRR_C_READ Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 FRR_C_VALUE FRR_C_VALUE 0x01 FRR_D_VALUE FRR_D_VALUE 0x02 FRR_A_VALUE FRR_A_VALUE 0x03 FRR_B_VALUE FRR_B_VALUE - Argument Fields:

- Reply Fields:

- Description:

- Value in Fast Response Register C.

- Type:

- U8

- Description:

- Value in Fast Response Register D.

- Type:

- U8

- Description:

- Value in Fast Response Register A.

- Type:

- U8

- Description:

- Value in Fast Response Register B.

- Type:

- U8

FRR_D_READ

- Number: 0x57

- Summary: Reads the fast response registers (FRR) starting with FRR_D.

- Purpose:

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- The FRR registers may be read in a burst fashion through the FRR_X_READ commands. After the initial 16 clock cycles, each additional eight clock cycles will clock out the contents of the next fast response register in a circular fashion. Example: If the FRR_A_READ command is issued, the registers will be read in the order A-B-C-D, while if the FRR_B_READ command is issued, the registers will be read in the order B-C-D-A, etc.

- This command does not cause CTS to go low, and can be sent and the reply read while CTS is low. The command ID should be clocked in on SDI then the reply should be clocked out on SDO without deasserting NSEL.

- The FRR_CTL_X_MODE properties are used to select the specific parameter values that will be returned by the FRR_X_READ commands. Please refer to the text description for FRR_CTL_X_MODE for more details regarding selection of the parameter(s) held within the FRR registers.

- The chip provides four Fast Response Registers (FRR) that may be read immediately without the need to monitor and check CTS, thus improving the speed at which the contents may be retrieved.

- Argument Stream:

FRR_D_READ Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x57 - Reply Stream:

FRR_D_READ Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 FRR_D_VALUE FRR_D_VALUE 0x01 FRR_A_VALUE FRR_A_VALUE 0x02 FRR_B_VALUE FRR_B_VALUE 0x03 FRR_C_VALUE FRR_C_VALUE - Argument Fields:

- Reply Fields:

- Description:

- Value in Fast Response Register D.

- Type:

- U8

- Description:

- Value in Fast Response Register A.

- Type:

- U8

- Description:

- Value in Fast Response Register B.

- Type:

- U8

- Description:

- Value in Fast Response Register C.

- Type:

- U8

TX_COMMANDS

START_TX

- Number: 0x31

- Summary: Switches to TX state and starts transmission of a packet.

- Purpose:

- This command switches the chip to TX state and begins transmission of a packet. Depending upon the value of the START parameter, the start of transmission may be delayed until a certain condition is met.

- Several optional parameters may be passed with this command. If these parameter values are not sent, their previously configured values remain in use. The parameter values are retained while in SLEEP mode, and thus only need to be written when they change.

- The chip may be configured to automatically enter a desired operational state after transmission of the packet.

- The chip will not return CTS high until the chip has entered the TX state.

- This command switches the chip to TX state and begins transmission of a packet. Depending upon the value of the START parameter, the start of transmission may be delayed until a certain condition is met.

- Argument Stream:

START_TX Argument Stream Index Name 7 6 5 4 3 2 1 0 0x00 CMD 0x31 0x01 CHANNEL CHANNEL 0x02 CONDITION TXCOMPLETE_STATE UPDATE RETRANSMIT START 0x03 TX_LEN 0 0 0 TX_LEN[12:8] 0x04 TX_LEN[7:0] 0x05 TX_DELAY TX_DELAY - Reply Stream:

START_TX Reply Stream Index Name 7 6 5 4 3 2 1 0 0x00 CTS CTS - Argument Fields:

- Description:

- Selects the channel number on which to transmit. Please refer to FREQ_CONTROL_CHANNEL_STEP_SIZE for more details regarding the channelized approach to frequency tuning of the chip.

- If the CHANNEL parameter byte is not passed with the command, the chip will tune to the last channel specified in either a START_TX or START_RX command; the internal variable that retains the CHANNEL value is shared by these two commands.

- Selects the channel number on which to transmit. Please refer to FREQ_CONTROL_CHANNEL_STEP_SIZE for more details regarding the channelized approach to frequency tuning of the chip.

- Type:

- U8

- Min:

- 0x0

- Max:

- 0xff

- Description:

- This parameter selects the desired operational state of the chip to automatically enter upon completion of the packet transmission.

- If this parameter is not passed with the command, the chip continues to use the previously configured value. If no value has been previously configured (i.e., upon POWER_UP), the default value of 3 = READY state is used.

- This parameter selects the desired operational state of the chip to automatically enter upon completion of the packet transmission.

- Format:

- Enumeration