# UBX-G6010, UBX-G6000/UBX-G0010 u-blox 6 single chips and chipsets Data Sheet

#### **Abstract**

Technical Data Sheet describing the UBX-G6010 and UBX-G6000/UBX-G0010 single chip and chipset GPS receivers. Featuring the high-performance u-blox 6 GPS position engine, the UBX-G6010 and UBX-G6000/UBX-G0010 require no external host and provide high sensitivity and fast acquisition/tracking times at low cost and power consumption.

Features include intelligent, user configurable power management, support for YUMA Capture & Process technology and support for u-blox' AssistNow Online and AssistNow Offline A-GPS services.

The UBX-G6010 and UBX-G6000/UBX-G0010 are available in 8x8 mm single-chip or 9x9 & 4x4 mm dual-chip packages.

www.u-blox.com

| Document Information |                                    |  |  |  |  |  |

|----------------------|------------------------------------|--|--|--|--|--|

| Title                | UBX-G6010, UBX-G6000/UBX-G0010     |  |  |  |  |  |

| Subtitle             | u-blox 6 single chips and chipsets |  |  |  |  |  |

| Document type        | Data Sheet                         |  |  |  |  |  |

| Document number      | GPS.G6-X-09004-B2                  |  |  |  |  |  |

| Document status      | s Preliminary                      |  |  |  |  |  |

| Document status information |                                                                                                               |  |  |  |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Objective<br>Specification  | This document contains target values. Revised and supplementary data will be published later.                 |  |  |  |  |  |  |

| Advance<br>Information      | This document contains data based on early testing. Revised and supplementary data will be published later.   |  |  |  |  |  |  |

| Preliminary                 | This document contains data from product verification. Revised and supplementary data may be published later. |  |  |  |  |  |  |

| Released                    | This document contains the final product specification.                                                       |  |  |  |  |  |  |

#### This document applies to the following products:

| Name                                               | Type number          | ROM/FLASH version | PCN reference |

|----------------------------------------------------|----------------------|-------------------|---------------|

| UBX-G6010<br>Single package                        | UBX-G6010-ST B0600 B | 6.02              | N/A           |

| (Standard)                                         |                      |                   |               |

| UBX-G6010                                          | UBX-G6010-SA B0600 B | 6.02              | N/A           |

| Single package (Automotive)                        |                      |                   |               |

| UBX-G6000<br>Baseband<br>Processor<br>(Automotive) | UBX-G6000-BA B0600   | 6.02              | N/A           |

| UBX-G0010<br>RF Front-End<br>(Automotive)          | UBX-G0010-QA B       |                   | N/A           |

This document and the use of any information contained therein, is subject to the acceptance of the u-blox terms and conditions. They can be downloaded from www.u-blox.com.

u-blox makes no warranties based on the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Reproduction, use or disclosure to third parties without express permission is strictly prohibited. Copyright © 2010, u-blox AG.

u-blox $^{\circ}$  is a registered trademark of u-blox Holding AG in the EU and other countries. ARM $^{\circ}$  is the registered trademark of ARM Limited in the EU and other countries.

GPS.G6-X-09004-B2 Page 2 of 53

# **Contents**

| Conte        | ents                                               | 3  |

|--------------|----------------------------------------------------|----|

| 1 Fu         | unctional description                              | 6  |

| 1.1          | Overview                                           | 6  |

| 1.2          | Highlights and features                            | 6  |

| Hi           | ighlights                                          | 6  |

| Fe           | eatures                                            | 6  |

| 1.3          | GPS performance                                    | 7  |

| 1.4          | Block diagrams                                     | 8  |

| 1.5          | Assisted GPS (A-GPS)                               | 9  |

| 1.6          | SuperSense Indoor GPS                              | 9  |

| 1.7          | KickStart / oscillators                            | 9  |

| 1.8          | GALILEO                                            | 9  |

| 1.9          | Capture & Process software and service from u-blox | 9  |

| 1.10         | Protocols and interfaces                           | 10 |

| 1.11         | Power management                                   | 10 |

| 2 <b>D</b> i | igital IC and mixed-signal subsystem               | 11 |

| 2.1          | Process engines                                    |    |

| 2.           | 1.1 Capture & Process                              |    |

| 2.2          | Peripherals                                        | 12 |

| 2.2          | 2.1 UART                                           | 12 |

| 2.2          | 2.2 USB                                            | 12 |

| 2.2          | 2.3 SPI                                            | 12 |

| 2.2          | 2.4 Display Data Channel (DDC)                     | 12 |

| 2.2          | 2.5 Peripheral Input Output (PIO)                  | 12 |

| 2.2          | 2.6 External Memory Interface (EMI)                | 12 |

| 2.2          | 2.7 Real-Time Clock (RTC) with backup RAM          | 13 |

| 2.2          | 2.8 Watchdog (WD)                                  | 13 |

| 2.2          | 2.9 Special Function Register (SF)                 | 13 |

| 2.2          | 2.10 Timer Counter (TC)                            | 13 |

| 2.3          | Analog blocks                                      | 13 |

| 2.3          | 3.1 Phase Lock Loop (PLL)                          | 13 |

| 2.3          | 3.2 Power Management Unit (PMU)                    | 13 |

| 3 R  | F su  | bsystem                              | 14 |

|------|-------|--------------------------------------|----|

| 4 P  | owe   | er management and operating modes    | 15 |

| 4.1  | Op    | perating modes                       | 15 |

| 4.   | 1.1   | Maximum Performance Mode             | 15 |

| 4.   | 1.2   | Eco Mode                             | 15 |

| 4.   | 1.3   | Power Save Mode                      | 15 |

| 4.2  | Ac    | equisition configuration             | 15 |

| 4.3  | Ва    | ase-band I/O supply voltage (VDD_IO) | 16 |

| 4.4  | Ca    | alculating power consumption         | 16 |

| 4.5  | Ex    | ternal DC/DC converter control       | 16 |

| 5 C  | onfi  | guration management                  | 17 |

| 5.1  | Co    | onfiguration pins                    | 17 |

| 6 Pi | in d  | efinition                            | 19 |

| 6.1  | Pir   | n assignment                         | 19 |

| 6.   | 1.1   | CVBGA100 / UBX-G6000-B               | 19 |

| 6.   | 1.2   | MLF24 / UBX-G0010-Q                  | 20 |

| 6.   | 1.3   | MLF56 / UBX-G6010-S                  | 21 |

| 6.2  | Pir   | n description                        | 22 |

| 7 El | lecti | rical specification                  | 31 |

| 7.1  | Ak    | osolute maximum rating               | 31 |

| 7.2  | Op    | perating conditions                  | 32 |

| 7.   | 2.1   | DC electrical characteristic         | 32 |

| 7.   | 2.2   | BB AC parameters                     | 33 |

| 7.   | 2.3   | RF AC parameters                     | 34 |

| 7.   | 2.4   | Power consumption                    | 35 |

| 7.3  | Ind   | dicative power requirements          | 35 |

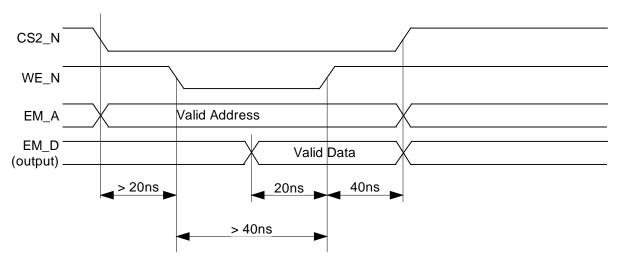

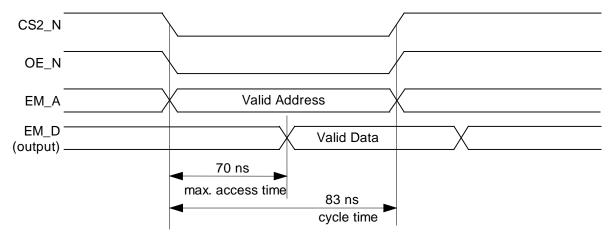

| 7.4  | ΕN    | All timing diagrams                  | 36 |

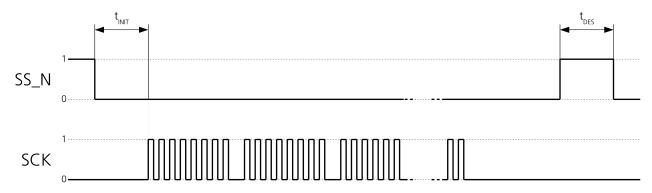

| 7.5  | SP    | PI timing diagrams                   | 37 |

| 7.6  | DE    | DC timing diagrams                   | 37 |

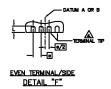

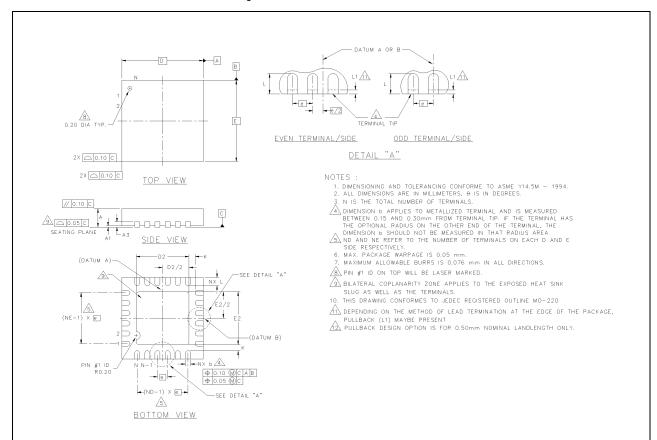

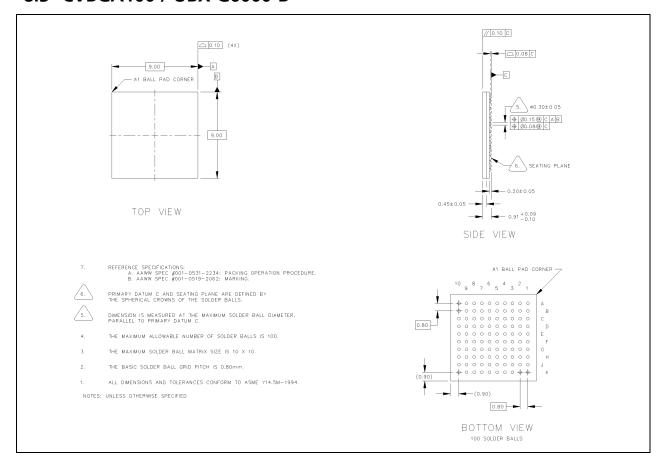

| 8 M  | lech  | anical specification                 | 38 |

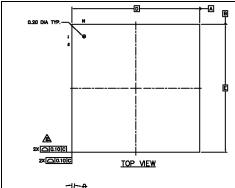

| 8.1  | М     | LF56 / UBX-G6010-S                   | 38 |

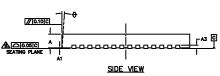

| 8.2  | М     | LF24 / UBX-G0010-Q                   | 39 |

| 8.3  | C١    | VBGA100 / UBX-G6000-B                | 40 |

| 9 Reliability tests and approvals    | 41 |

|--------------------------------------|----|

| 9.1 Reliability tests                | 41 |

| 9.2 Approvals                        | 41 |

| 10 Product handling                  | 42 |

| 10.1 Packaging                       | 42 |

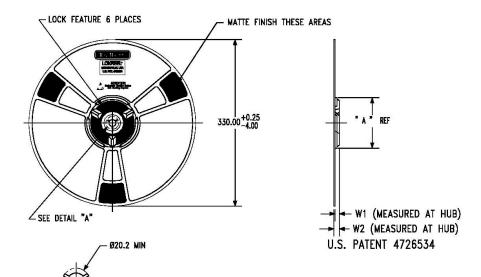

| 10.1.1 Reels                         | 42 |

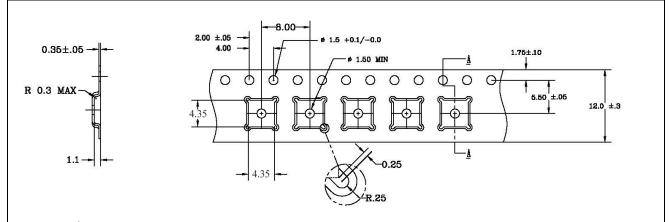

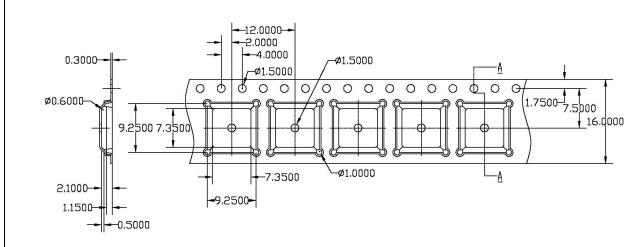

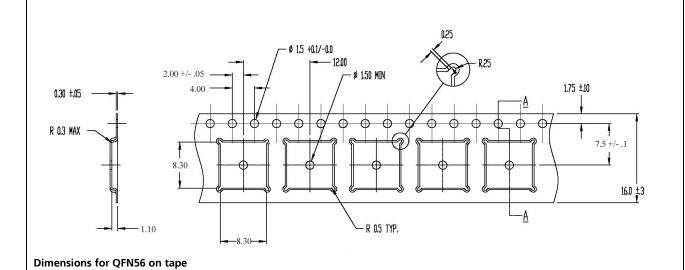

| 10.1.2 Tapes                         | 44 |

| 10.2 Shipment, storage and handling  | 45 |

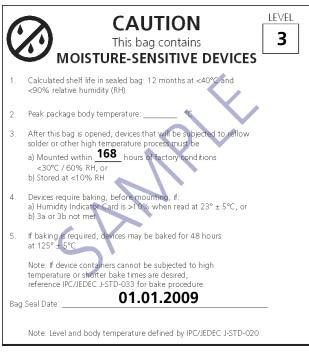

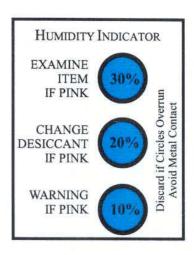

| 10.2.1 Moisture sensitivity levels   | 45 |

| 10.2.2 Shipment                      | 45 |

| 10.2.3 Storage and floor life        | 47 |

| 10.2.4 Drying                        | 47 |

| 10.2.5 Reflow soldering              | 47 |

| 10.2.6 ESD handling precautions      |    |

| 11 Default settings                  | 49 |

| 12 Labeling and ordering information | 50 |

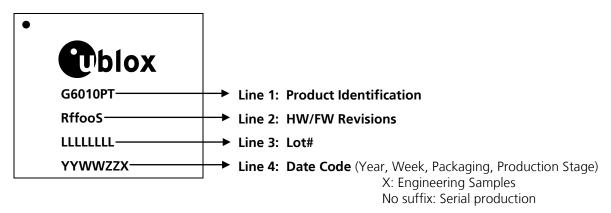

| 12.1 Product labeling                | 50 |

| 12.1.1 BGA100, MLF56                 | 50 |

| 12.1.2 MLF24                         | 50 |

| 12.2 Explanation of product codes    | 51 |

| 12.3 Ordering codes                  | 51 |

| Related documents                    | 52 |

| Revision history                     | 52 |

| Contact                              | 53 |

# 1 Functional description

#### 1.1 Overview

The UBX-G6010 and UBX-G6000/UBX-G0010 are the newest generation single chip and chipset GPS receivers from u-blox and demonstrate our continuing commitment to advancing GPS technology. Featuring the high performance u-blox-6 position engine, the UBX-G6010 and UBX-G6000/UBX-G0010 provide even better sensitivity and acquisition times while requiring no external host. Sophisticated RF-architecture and interference suppression ensure maximum performance even in GPS-hostile environments.

u-blox 6 technology has been designed with low power consumption and low costs in mind, and still delivers high performance GPS. Integrated Capture & Process¹ support and intelligent power management are breakthroughs for low-power applications. The minimal BOM requires as few as 19 passive components, an LDO and LNA are built in and costly external memory is not needed. Lower price GPS crystals as well as TCXOs are supported, and 2-layer PCB integration capability and small footprint ensure further cost savings. The UBX-G6010 is the ideal solution for cost sensitive applications that don't require firmware update capability, while the UBX-G6000/UBX-G0010 supports external memory where firmware update capability is required.

## 1.2 Highlights and features

## **Highlights**

- u-blox 6 position engine with over 2 million effective correlators featuring < 1 s acquisition, –147 dBm coldstart acquisition sensitivity and 5 Hz update rate

- Supports ultra-low power logging and geo-tagging applications with Capture & Process (<0.2 s capture time)</li>

- Intelligent, user configurable power management for radically lower power consumption

- Supports u-blox' AssistNow Online / AssistNow Offline A-GPS services and is OMA SUPL compliant

- GALILEO ready

- Automotive qualified

- Minimal BOM costs

#### **Features**

|                        | Chip Size (mm) | ТСХО | GPS Crystal | FW Update<br>/ FLASH | Power Save<br>mode | UART | USB | SPI | DDC | Capture & Process | AssistNow<br>Online | AssistNow<br>Offline | Dead Reckoning | Raw Data | Precision Timing | Timepulse | CFG Pins | Reset Input | Antenna<br>Supply | Antenna<br>Supervisor |

|------------------------|----------------|------|-------------|----------------------|--------------------|------|-----|-----|-----|-------------------|---------------------|----------------------|----------------|----------|------------------|-----------|----------|-------------|-------------------|-----------------------|

| UBX-G6010              | 8x8            | 0    | •           |                      | •                  | 1    | 1   | 1   | 1   | •                 | •                   | •                    |                |          |                  | 2         | 10       | •           | •                 | •                     |

| UBX-G6000<br>UBX-G0010 | 9x9<br>4x4     | 0    | •           | F                    | •                  | 2    | 1   | 1   | 1   | •                 | •                   | •                    |                |          |                  | 2         | 12       | •           | •                 | •                     |

F = Requires external FLASH, O = Optional

Table 1: Features of UBX-G6010 and UBX-G6000/UBX-G0010

<sup>&</sup>lt;sup>1</sup> Capture & Process is u-blox' patented technology featuring ultra-fast position capture and ultra-low power consumption. The separately available software product YUMA is required for implementation of Capture & Process technology.

# 1.3 GPS performance

| Parameter                                 | Specification                                                                  |                           |                             |

|-------------------------------------------|--------------------------------------------------------------------------------|---------------------------|-----------------------------|

| Receiver type                             | 50 Channels<br>GPS L1 frequency, C/A Code<br>GALILEO Open Service L1 frequency |                           |                             |

| Time-To-First-Fix <sup>2</sup>            |                                                                                | TCXO                      | Crystal                     |

|                                           | Cold Start (Autonomous)                                                        | 29 s                      | 32 s                        |

|                                           | Warm Start (Autonomous)                                                        | 29 s                      | 32 s                        |

|                                           | Hot Start (Autonomous)                                                         | <1 s                      | <1 s                        |

|                                           | Aided Starts <sup>3</sup>                                                      | <1 s                      | <3 s                        |

|                                           | Capture Time (Capture & Process)                                               | <0.2 s                    | <0.2 s                      |

| Sensitivity <sup>4</sup>                  |                                                                                | TCXO                      | Crystal                     |

| ,                                         | Tracking & Navigation                                                          | -160 dBm                  | -160 dBm                    |

|                                           | Reacquisition                                                                  | -160 dBm                  | -160 dBm                    |

|                                           | Cold Start (Autonomous)                                                        | -147 dBm                  | -146 dBm                    |

| Horizontal position accuracy <sup>5</sup> | Autonomous                                                                     | < 2.5 m                   |                             |

|                                           | SBAS                                                                           | < 2.0 m                   |                             |

| Accuracy of Timepulse signal              | RMS                                                                            | 30 ns                     |                             |

|                                           | 99%                                                                            | <60 ns                    |                             |

|                                           | Time Pulse                                                                     |                           | 1 kHz (Tp = 1/f = 4 s 1 ms) |

| Max navigation update rate                |                                                                                | up to 5Hz (ROM) / 2Hz FLA | SH                          |

| Velocity accuracy <sup>6</sup>            |                                                                                | 0.1m/s                    |                             |

| Heading accuracy <sup>7</sup>             |                                                                                | 0.5 degrees               |                             |

| Dynamics                                  |                                                                                | ≤ 4 g                     |                             |

| Operational limits <sup>8</sup>           | Altitude                                                                       | 50000 m                   |                             |

| •                                         | Velocity                                                                       | 500 m/s                   |                             |

Table 2: GPS performance

Functional description

<sup>&</sup>lt;sup>2</sup> All satellites at -130 dBm

<sup>&</sup>lt;sup>3</sup> Dependent on aiding data connection speed and latency

<sup>&</sup>lt;sup>4</sup> Demonstrated with a good active antenna

<sup>&</sup>lt;sup>5</sup> CEP, 50%, 24 hours static, -130dBm, SEP: <3.5m

<sup>6 50% @ 30</sup> m/s

<sup>&</sup>lt;sup>7</sup> 50% @ 30 m/s

<sup>&</sup>lt;sup>8</sup> Assuming Airborne <4g platform

# 1.4 Block diagrams

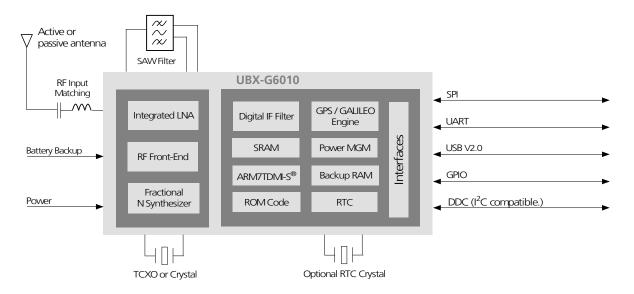

Figure 1: UBX-G6010 single-chip GPS receiver: block diagram

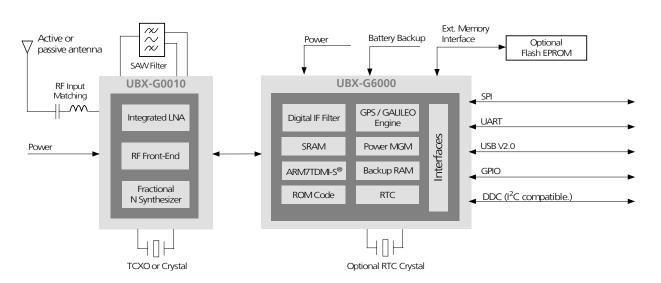

Figure 2: UBX-G0010 / UBX-G6000 dual-chip GPS receiver: block diagram

## 1.5 Assisted GPS (A-GPS)

Supply of aiding information like ephemeris, almanac, rough last position and time and satellite status and an optional time synchronization signal will reduce time to first fix significantly and improve the acquisition sensitivity. All u-blox 6 ICs support the u-blox AssistNow Online and AssistNow Offline A-GPS services and are OMA SUPL compliant.

## 1.6 SuperSense Indoor GPS

All u-blox 6 ICs come with SuperSense, providing ultra-fast acquisition/reacquisition and exceptional tracking sensitivity. SuperSense enables best-in-class tracking and navigation in difficult signal environments such as urban canyons or indoor locations.

#### 1.7 KickStart / oscillators

A feature available with u-blox 6 is KickStart. This functionality uses a TCXO to accelerate weak signal acquisition, enabling faster start and reacquisition times.

#### 1.8 GALILEO

u-blox 6 receivers receive and track GPS and GALILEO signals simultaneously, enhancing accuracy and coverage. When GALILEO-L1 signals become available, u-blox 6 receivers equipped with FLASH memory will be capable of receiving and processing them via a simple upgrade. The ability to receive and track GALILEO satellite signals will result in higher coverage, improved reliability and better accuracy.

## 1.9 Capture & Process software and service from u-blox

Capture & Process is a different way of calculating GPS position, where the location is not needed immediately, but somewhere later in time. The benefits of this technology lie in not needing to download the slowly transmitted satellite information data from GPS signal at the time of capture, but providing it at the user's convenience through an internet link to the processing software. This results in extremely short times (<0.2s) to create a snapshot of the GPS signal ("Capture") and thus very low power consumption. It also frees the user from having to wait until satellite information data is available.

Depending on the use-case, either realtime-GPS with standalone position calculation or Capture & Process with subsequent position calculation provide the greatest advantage to the user.

The two steps for Capture & Process are:

- 1. Capture: perform a single or multiple captures on a mobile device with a u-blox' GPS receiver, and transfer the data (typically 120 kByte per capture) to an application processor which can store it on a mass storage device.

- 2. Process: connect the storage device to a MAC or PC which is connected to the internet, and use u-blox' YUMA software to calculate position from the snapshot from the GPS receiver and the data provided by u-blox' online service.

YUMA is the software and service component of u-blox' Capture & Process technology. u-blox 6 features a powerful hardware to capture raw GPS signal data required by YUMA, and has very low demands on the application processor in terms of supported interfaces and their speed. Data transfer to the application processor is possible via UART, USB, SPI and DDC (I2C) interfaces.

YUMA is particularly useful for mobile logging and tracking applications where low power consumption is critical, and is a must for photo geotagging capability with cameras. Other applications include bike computers, waypoint loggers, asset/animal trackers, etc.

#### 1.10 Protocols and interfaces

| Protocol | Туре                                               |

|----------|----------------------------------------------------|

| NMEA     | Input/output, ASCII, 0183, 2.3 (compatible to 3.0) |

| UBX      | Input/output, binary, u-blox proprietary           |

#### **Table 3: Available Protocols**

Both protocols are available on UART, USB, DDC and SPI. For specification of the various protocols see the *u-blox 5 & u-blox 6 Receiver Description Including Protocol Specification* [2].

## 1.11 Power management

u-blox 6 technology offers power optimized architecture with built-in autonomous power saving functions that minimize power consumption at any given time. The receiver can be operated in 2 different continuous operating modes: Maximum Performance, and Eco Mode. In addition an intermittent Power Save Mode allows reducing the average tracking current consumption by periodically switching off parts of or the complete GPS receiver and waking it up at configurable intervals. For more information, see *Chapter 4*

# 2 Digital IC and mixed-signal subsystem

The baseband-IC integrates an ARM7TDMI-S™ CPU and all the memory required for embedded firmware execution. Specific hardware required for signal acquisition and tracking and a wide selection of peripheral interfaces are provided. Analog functional blocks such as PLL, A/D converters and Power Management Unit (PMU) are fully integrated. u-blox 6's embedded firmware provides all the algorithms needed to calculate navigation data output.

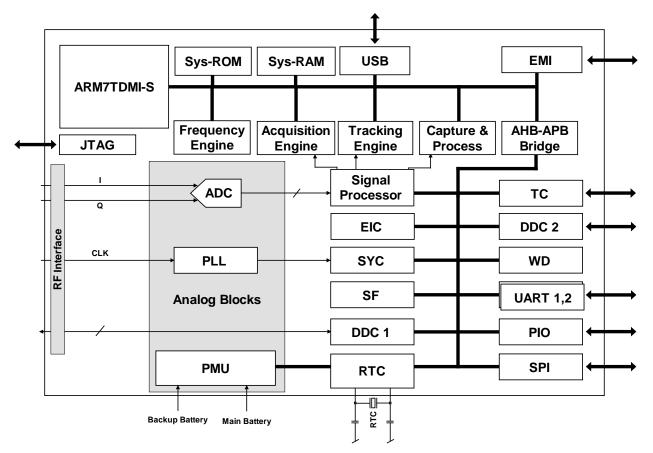

Figure 3 shows the block diagram for the baseband-IC. Selected functional blocks are described in the following sections.

Figure 3: u-blox 6 Baseband-IC block diagram

# 2.1 Process engines

#### 2.1.1 Capture & Process

The Capture & Process functional block supports u-blox' Capture & Process technology (see section 1.9).

## 2.2 Peripherals

A number of peripheral interfaces are provided. The embedded firmware uses these interfaces according to their respective protocol specifications. For specific applications, the firmware also supports the connection of peripheral devices, such as external memories or sensors, to some of the interfaces.

#### 2.2.1 **UART**

The baseband-IC has two UART interfaces, both of which can be used for position transmission. These ports support NMEA and UBX protocols at different baud rates. The useable low end baudrates depend on user requested communication traffic. For supported baudrates see the *u-blox 5 & u-blox 6 Receiver Description Including Protocol Specification* [2].

The UART configuration can be defined at system start-up through configuration pins or settings stored permanently in any non-volatile memory attached to the baseband-IC. Note that only one UART is available on the UBX-G6010.

#### 2.2.2 USB

A USB version 2.0 FS (Full Speed, 12Mbit/s) interface can be used as an alternative to the UART. The pull-up resistor on DP is integrated to signal a full-speed device to the host. The VDD\_USB pin supplies the USB interface, independently from the VDD\_IO pin.

#### 2.2.3 SPI

The SPI allows for the connection of external devices with a serial interface, e.g. FLASH memories or A/D converters, or to interface to a host CPU. The interface can be operated in master or slave mode. In master mode, one chip select signal is available to select external slaves. In slave mode a single chip select signal enables communication with the host.

SPI FLASH is supported for AssistNow Offline data and to store the receiver configuration.

#### 2.2.4 Display Data Channel (DDC)

Two independent DDC interfaces are available. One is used exclusively for communication with the RF-IC.

The second interface can be used either to access external devices with a serial interface, e.g. EEPROM or A/D converters, or to interface with a host CPU. It is capable of master and slave operation. The DDC protocol and electrical interface are fully compatible with Standard-Mode of the I<sup>2</sup>C industry standard.

#### 2.2.5 Peripheral Input Output (PIO)

The PIO block has two basic functions:

- It maps peripheral functions to the I/O pins. The configuration of the pin is determined by the peripheral function.

- It allows the use of I/O pins as general-purpose I/O.

Optionally pull-up or pull-down resistors can be enabled separately for each pin.

#### 2.2.6 External Memory Interface (EMI)

The external memory interface is used to connect to external FLASH memory. Up to 32 Mbit size 16-bit wide memories can be connected. Address lines EM\_A18...EM\_A21 are shared with PIO functions. EMI is only available with the UBX-G6000-B.

#### 2.2.7 Real-Time Clock (RTC) with backup RAM

The RTC is driven by its own 32 kHz oscillator and is, together with the 4 KB backup RAM, powered by the VDD\_B back-up supply voltage. When the engine is in a power-saving mode or when the battery is low, part of the baseband switches off. The RTC provides a timing reference at these times, which enables all relevant data to be saved in the backup RAM to allow later a Hot-Start.

The RTC crystal is optional as it is required in stand-alone applications where hot or warm starts are enabled. It is also required for using Power Save Mode. In these cases, actual time is maintained in the RTC and Ephemeris and other last known data is kept in the backup RAM. In A-GPS based systems, the RTC is not required and coarse or fine time information is available from the network. If neither backup RAM nor RTC are required, V BCKP should be connected to GND.

#### 2.2.8 Watchdog (WD)

u-blox 6 includes a Watchdog timer, that prevents system-lockups caused when the software gets trapped in a deadlock. During normal operation, the firmware resets the watchdog's internal counter at regular intervals before timer overflow occurs.

#### 2.2.9 Special Function Register (SF)

This register contains chip version and boot configuration read from SAFEBOOT\_N and CFG\_PIN pins.

#### 2.2.10 Timer Counter (TC)

Timer counter has two TIMEMARK inputs and two TIMEPULSE outputs.

TIMEMARK inputs (routed through EXTINTO and EXTINT1) time external events relative to GPS time.

TIMEPULSE outputs generate pulse trains synchronized with GPS or UTC time grid with intervals configurable over a wide frequency range. Thus one TIMEPULSE output may be used as a low frequency time synchronization pulse while the other is being used as a high frequency reference frequency.

All in- and output signals are synchronized with the receiver internal clock frequency of 48 MHz, resulting in an inherent maximum quantization error of in- and output signals of  $\pm$ 10 ns.

# 2.3 Analog blocks

#### 2.3.1 Phase Lock Loop (PLL)

The fully integrated low-power fractional sigma-delta PLL generates the master clock frequency from a wide selection range of reference frequencies supplied at the differential CLK input.

#### 2.3.2 Power Management Unit (PMU)

The PMU provides all required supply voltages to the system. A number of configurations are possible:

- A single supply voltage can be used for the complete system.

- The RF and baseband sections can be supplied by different voltage sources.

The PMU also generates the supply voltage for the TCXO, if used. However the TCXO specification may affect the system supply voltage range.

When the battery level is too low for proper system operation, the PMU will automatically switch off all blocks but the backup section of the baseband-IC containing the RTC and the backup RAM. A separate backup-battery may be connected to the baseband for supplying V\_BCKP in case the main voltage V\_RUN is not available.

# 3 RF subsystem

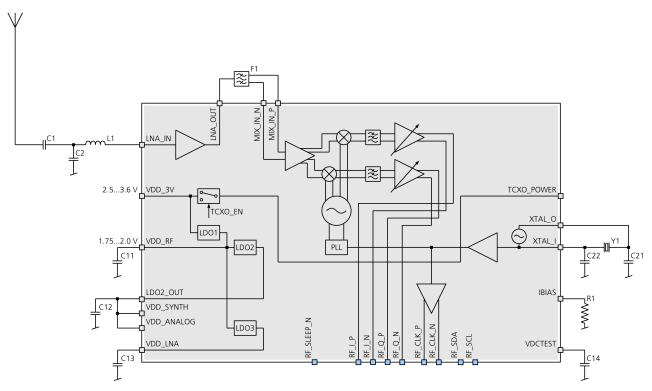

The RF-IC receiver implements a low-IF architecture with a 3 MHz intermediate frequency. The input signal is a 6MHz wide portion of the spectrum centered on the L1 GPS/GALILEO band at 1575.42 MHz. The received signal is amplified by a single-ended 50 Ohm-matched low-noise amplifier, and then fed to an external SAW filter with a 50 Ohm input impedance. The SAW filter provides a single-ended to differential conversion and has a 100 Ohm differential output impedance. A differential RF amplifier, input matched to 100 Ohm, offers further amplification, thus reducing the noise figure requirements for the I and Q mixers. After down-conversion, the I and Q signals are low-pass filtered and amplified by a Programmable Gain Amplifier (PGA). The differential I and Q signals are then sent to the baseband IC, where A/D conversion, signal processing and final image rejection are performed.

Figure 4: RF IC block diagram

# 4 Power management and operating modes

# 4.1 Operating modes

u-blox-6 ICs have 2 continuous operating modes (Maximum Performance Mode and Eco Mode) and 1 intermittent operating mode (Power Save Mode). Maximum Performance Mode freely uses the acquisition engine, resulting in the best possible TTFF, while Eco Mode optimizes the use of the acquisition engine to deliver lower current consumption. At medium to strong signals, there is almost no difference for acquisition and tracking performance in these modes.

#### 4.1.1 Maximum Performance Mode

In Maximum Performance mode, u-blox 6 receivers use the acquisition engine at full performance to search for all possible satellites until the Almanac is completely downloaded.

As a consequence, tracking current consumption level will be achieved when:

- A valid GPS position is fixed

- Almanac is entirely downloaded

- Ephemeris for all satellites in view are valid

#### 4.1.2 Eco Mode

In Eco Mode, u-blox 6 receivers use the acquisition engine to search for new satellites only when needed for navigation:

- In cold starts, u-blox 6 searches for enough satellites to navigate and optimizes use of the acquisition engine to download their ephemeris.

- In non-cold starts, u-blox 6 focuses on searching for visible satellites whose orbits are known from the Almanac.

In Eco Mode, the u-blox 6 acquisition engine limits use of its searching resources to minimize power consumption. As a consequence the time to find some satellites at weakest signal level might be slightly increased in comparison to Maximum Performance Mode.

u-blox 6 deactivates the acquisition engine as soon as a position is fixed and a sufficient number (at least 4) of satellites are being tracked. The tracking engine continues to search and track new satellites without orbit information.

#### 4.1.3 Power Save Mode

u-blox 6 ICs include power saving options that allow reducing the average tracking current consumption by periodically switching off parts of or the complete GPS receiver and waking it up at configurable intervals from one second to one week. This can be done by using a hardware interrupt or by sending a serial command.

For more information about power management strategies, see the *u-blox 5 & u-blox 6 Receiver Description Including Protocol Specification* [2] and the *Power Management Considerations Application Note* [4].

# 4.2 Acquisition configuration

u-blox 6 positioning technology allows configuration of the acquisition engine to a slower update rate, which can reduce power consumption. This can in some situations result in a longer TTFF.

For more information see the u-blox 5 & u-blox 6 Receiver Description Including Protocol Specification [2].

# 4.3 Base-band I/O supply voltage (VDD\_IO)

The digital I/Os of the baseband part are supplied with VDD\_IO from the host system. The wide range of VDD\_IO allows seamless interfacing to standard logic voltage levels independently of the baseband supply voltage level. Without VDD\_IO supply the system will be kept in reset state.

## 4.4 Calculating power consumption

See the Power Management Considerations Application Note [4].

#### 4.5 External DC/DC converter control

Pin DCDC\_EN enables external DC/DC converter.

# 5 Configuration management

System configuration goes through multiple steps. The hierarchy of the information found at different sources is as follows:

- 1. Actual configuration in system RAM

- 2. Configuration in backup RAM

- 3. Configuration in FLASH memory

- 4. Configuration in serial EEPROM

- 5. Configuration through CFG pins

- 6. Default (ROM) settings

During system boot, the system first starts from the ROM default settings. Then it tries to find out where the actual configuration can be found, i.e. it searches for EEPROM, FLASH and/or backup RAM and looks for valid contents. Thus, a search tree can be built and any configuration setting that is needed by the firmware is searched downwards from the most actual (system RAM) to the most outdated (system ROM) information. The system uses the first valid information it finds.

# 5.1 Configuration pins

Some PIO pins are read at system start and can be used to submit some start-up configuration into the boot process. In the following tables, all default settings (pin left open) are **bold**.

The first step is to analyze the SAFEBOOT\_N pin. If it is pulled to low level, the system will start up in safe mode using as few configuration settings as possible and establishing only the minimum functionality required for establishing communication with the host. No GPS operation is started. This mode is primarily used for production testing.

The state of SAFEBOOT\_N at system start is preserved in bit BOOTMODEO of the special function register (SF).

| SAFEBOOT_N |                                                         |

|------------|---------------------------------------------------------|

| 1          | Normal Boot                                             |

| 0          | Safe Mode, minimal ROM boot, Ignore Backup RAM & FLASH. |

#### **Table 4: SAFEBOOT configuration**

The CFG\_PIN decides whether external parallel FLASH memory is accessed at all. If the CFG\_PIN is left open (i.e. = 1) at power up the receiver reads the configuration from the configuration pins.

The detection of serial FLASH on SPI and serial EEPROM on DDC interfaces is not affected by CFG\_PIN. In default, only pin configurations will be read.

The state of CFG\_PIN at system start is preserved in bit BOOTMODE1 of the special function register (SF).

| CFG_PIN |                                                      |

|---------|------------------------------------------------------|

| 1       | Use CFG pins                                         |

| 0       | Ignore CFG pins, required setting for parallel Flash |

**Table 5: Pin configuration**

For more information about configuration consult the *UBX-G6010*, *UBX-G6000/UBX-G0010 Hardware Integration Manual* [1].

CFG\_CLK determines GPS clock frequency.

| CFG_CLK2 | CFG_CLK1 | CFG_CLK0 | Reference Frequency |

|----------|----------|----------|---------------------|

| 1        | 1        | 1        | 26 MHz              |

| 1        | 1        | 0        | 38.4 MHz            |

| 1        | 0        | 1        | 33.6 MHz            |

| 1        | 0        | 0        | 19.2 MHz            |

| 0        | 1        | 1        | 16.8 MHz            |

| 0        | 1        | 0        | Reserved            |

| 0        | 0        | 1        | Reserved            |

| 0        | 0        | 0        | Reserved            |

Table 6: Reference GPS clock configuration

Refer to Table 30 for AC parameter frequency range limitations applicable to XTAL and TCXO operation, respectively.

The communication interfaces (UART1/2, USB, SPI, DDC) can be configured in terms of protocol and baud rate.

| CFG_COM1 | CFG_COM0 | Protocol | Messages                                                                    | UART1/2<br>Baud rate | USB Power          |

|----------|----------|----------|-----------------------------------------------------------------------------|----------------------|--------------------|

| 1        | 1        | NMEA     | GSV, RMC, GSA, GGA, GLL, VTG, TXT                                           | 9600                 | <b>BUS Powered</b> |

| 1        | 0        | NMEA     | GSV, RMC, GSA, GGA, GLL, VTG, TXT                                           | 38400                | Self Powered       |

| 0        | 1        | NMEA     | GSV <sup>9</sup> , RMC, GSA, GGA, VTG, TXT                                  | 4800                 | BUS Powered        |

| 0        | 0        | UBX      | NAV-SOL, NAV-STATUS, NAV-SVINFO, NAV-CLOCK, INF,<br>MON-EXCEPT, AID-ALPSERV | 57600                | BUS Powered        |

**Table 7: COM configuration**

The strategy of the GNSS receiver management can be optimized according to several different operation modes. The goal is to adapt power consumption and responsiveness, as well as sensitivity, to a given application.

| CFG_GPS2 | CFG_GPS1 | CFG_GPS0 | GPS mode                         |

|----------|----------|----------|----------------------------------|

| 1        | 1        | 1        | Maximum Performance Mode TCXO    |

| 1        | 1        | 0        | Eco Mode TCXO                    |

| 1        | 0        | 1        | Reserved                         |

| 1        | 0        | 0        | Capture & Process boot mode TCXO |

| 0        | 1        | 1        | Maximum Performance Mode XTO     |

| 0        | 1        | 0        | Eco Mode XTO                     |

| 0        | 0        | 1        | Reserved                         |

| 0        | 0        | 0        | Capture & Process boot mode XTO  |

Table 8: GPS operation configuration

There are additional configuration pins reserved for further use, identified by pin name CFG\_FFUx. Do not connect these pins unless pins are used for another secondary function.

GPS.G6-X-09004-B2 Preliminary Page 18 of 53

<sup>&</sup>lt;sup>9</sup> every 5<sup>th</sup> fix

# 6 Pin definition

# 6.1 Pin assignment

Figure 5/Table 9, Figure 6 and Figure 7 show the pin assignments of the CVBGA, MLF24 and MLF56 chips respectively. Note that the signal names are linked to the corresponding description tables.

Some pins have shared functions. Use special care when designing with these pins since overall function and configuration of the device can be affected.

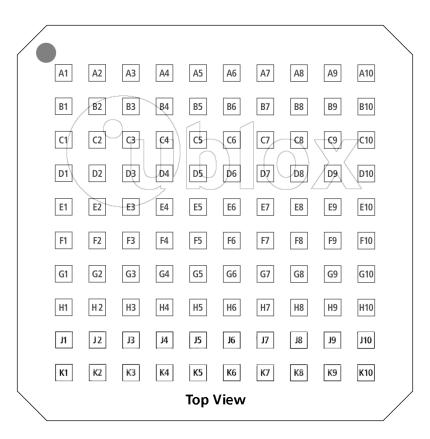

#### 6.1.1 CVBGA100 / UBX-G6000-B

Figure 5: CVBGA (UBX-G6000-B) top view

|   | 1                     | 2                                 | 3                   | 4                                               | 5                            | 6                     | 7                 | 8                          | 9                              | 10                              |

|---|-----------------------|-----------------------------------|---------------------|-------------------------------------------------|------------------------------|-----------------------|-------------------|----------------------------|--------------------------------|---------------------------------|

| Α | RTC_XTAL_I            | BB_SLEEP_N                        | BB_CLK_P            | BB_I_N                                          | BB_Q_N                       | EM_A9                 | EM_D8             | CFG_PIN /<br>TMS           | EM_A6                          | TCK                             |

| В | RTC_XTAL_O            | VSS_PLL                           | BB_CLK_N            | BB_I_P                                          | BB_Q_P                       | EM_D15                | EM_D9             | EM_A7                      | PIO13 /<br>CFG_CLK0 /<br>EM_A0 | PIO17 /<br>CFG_FFU2 /<br>EM_A20 |

| С | VDD_PLL               | EM_D11                            | PIO23 /<br>CFG_GPS2 | PIO0 /<br>BB_SDA                                | Not<br>connected             | WE_N                  | EM_A3             | TIMEPULSE /<br>TDO         | SAFEBOOT_N<br>/ TDI            | EM_A2                           |

| D | EM_A11                | PIO22 /<br>CFG_GPS1               | PIO1<br>BB_SCL      | Not<br>connected                                | PIO7 /<br>EXTINTO            | PIO8 /<br>EXTINT1     | EM_A5             | CS2_N                      | EM_A1                          | OE_N                            |

| E | EM_A10                | EM_A12                            | GND                 | GND                                             | GND                          | GND                   | EM_D10            | VDD_IO1                    | EM_A4                          | PIO16 /<br>CFG_FFU0 /<br>EM_A19 |

| F | EM_A14                | EM_A15                            | EM_D14              | EM_D4                                           | GND                          | GND                   | GND               | PIO6 /<br>SS_N /<br>SCSO_N | PIO14 /<br>CFG_CLK1            | PIO15 /<br>CFG_CLK2 /<br>EM_A18 |

| G | EM_A16                | PIO12 /<br>ANT_SHORT_<br>N / RXD2 | VDD_USB             | EM_A8                                           | EM_D6                        | PIO9 /<br>PER_RESET_N | PIO4 /<br>RXD1    | VDD_C1                     | EM_D0                          | PIO24 /<br>CFG_FFU1             |

| Н | PIO10 /<br>ANT_DETECT | PIO11/<br>ANT_OFF /<br>TXD2       | EM_A17              | PIO18 /<br>CFG_FFU3 /<br>EM_A21 /<br>TIMEPULSE2 | EM_D5                        | PIO5 /<br>TXD1        | Do not<br>connect | PIO2 /<br>SDA2             | EM_D7                          | PIO3 /<br>SCL2                  |

| J | EM_A13                | USB_DM                            | VDD_C0              | EM_D12                                          | EM_D3                        | EM_D1                 | V_RESET           | DCDC_EN                    | V_RUN                          | PIO19 /<br>CFG_COM0 /<br>MOSI   |

| K | USB_DP                | VDD_IO0                           | EM_D13              | PIO20 /<br>CFG_COM1<br>/ MISO                   | PIO21 /<br>CFG_GPS0 /<br>SCK | EM_D2                 | V_TH              | V_DCDC                     | V_BCKP                         | VDD_B                           |

Table 9: Pin assignment CVBGA (UBX-G6000)

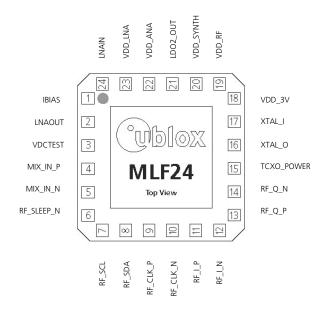

#### 6.1.2 MLF24 / UBX-G0010-Q

Figure 6: Pin assignment MLF24 (UBX-G0010-Q)

Signal names are linked to the corresponding description tables. For multiple function pins, select the specific signal.

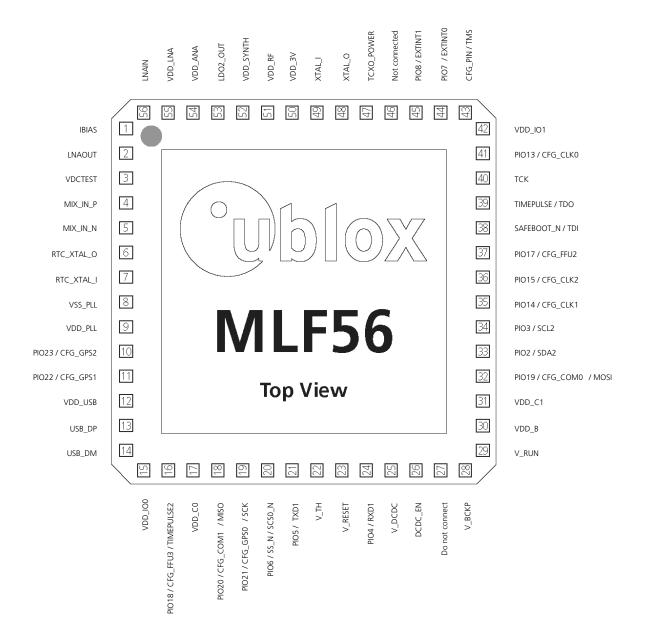

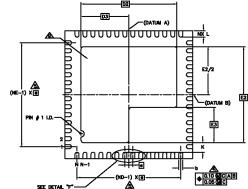

#### 6.1.3 MLF56 / UBX-G6010-S

Figure 7: Pin assignment MLF56 (UBX-G6010-S)

Signal names are linked to the corresponding description tables. For multiple function pins, select the specific signal.

# 6.2 Pin description

| Name       | Pin<br>CVBGA               | Pin<br>MLF56 | Pin<br>MLF24      | Power<br>Domain | I/O<br>Reset  | I/O<br>Core off     | Description                 |

|------------|----------------------------|--------------|-------------------|-----------------|---------------|---------------------|-----------------------------|

| V_DCDC     | K8                         | 25           | -                 | VDD_B           |               |                     | Main Core Supply            |

| V_RUN      | J9                         | 29           | -                 | VDD_B           |               |                     | Main Backup Supply          |

| V_BCKP     | K9                         | 28           | -                 | VDD_B           |               |                     | Backup Cell Supply          |

| VDD_B      | K10                        | 30           | -                 | VDD_B           |               |                     | Backup Power                |

| VDD_C0     | J3                         | 17           | -                 | VDD_C           |               |                     | Core Power                  |

| VDD_C1     | G8                         | 31           | -                 | VDD_C           |               |                     | Core Power                  |

| VDD_IO0    | K2                         | 15           | -                 | VDD_IO          |               |                     | I/O Ring Power              |

| VDD_IO1    | E8                         | 42           | -                 | VDD_IO          |               |                     | I/O Ring Power              |

| VDD_USB    | G3                         | 12           | -                 | VDD_USB         |               |                     | USB Power                   |

| VDD_PLL    | C1                         | 9            | -                 | VDD_PLL         |               |                     | PLL Power                   |

| V_RESET    | J7                         | 23           | -                 | VDD_B           |               |                     | Supply Monitor Analog       |

| V_TH       | K7                         | 22           | -                 | VDD_B           |               |                     | Reset Threshold Analog      |

| DCDC_EN    | J8                         | 26           | -                 | VDD_IO          | Output<br>Low | Input Pull-<br>Down | DC/DC Control Output        |

| VSS_B0     |                            |              | -                 | VDD_B           |               |                     | Ground                      |

| VSS_B1     |                            |              | -                 | VDD_B           |               |                     | Ground                      |

| VSS_C0     |                            |              | -                 | VDD_C           |               |                     | Ground                      |

| VSS_C1     | E3, E4, E5,<br>E6, F5, F6, |              | -                 | VDD_C           |               |                     | Ground                      |

| VSS_C2     | F7                         | Center       | -                 | VDD_C           |               |                     | Ground                      |

| VSS_IO0    |                            | GND Pad      | -                 | VDD_IO          |               |                     | Ground                      |

| VSS_IO1    |                            |              | -                 | VDD_IO          |               |                     | Ground                      |

| VSS_USB    |                            |              | -                 | VDD_USB         |               |                     | Ground                      |

| VSS_RF     | -                          |              | Center<br>GND Pad |                 |               |                     | Ground                      |

| VSS_PLL    | B2                         | 8            | -                 |                 |               |                     | PLL Analog Reference Ground |

| IBIAS      | -                          | 1            | 1                 |                 |               |                     | Reference Current Analog    |

| LDO2_OUT   | -                          | 53           | 21                |                 |               |                     | LDO2 Output                 |

| TCXO_POWER | -                          | 47           | 15                |                 |               |                     | TCXO Bias Current           |

| VDD_3V     | -                          | 50           | 18                |                 |               |                     | RF Main Supply              |

| VDD_ANA    | -                          | 54           | 22                |                 |               |                     | Analog Power                |

| VDD_LNA    | -                          | 55           | 23                |                 |               |                     | LNA Power Supply            |

| VDD_RF     | -                          | 51           | 19                |                 |               |                     | RF Core Power               |

| VDD_SYNTH  | -                          | 52           | 20                |                 |               |                     | Synthesizer Power           |

**Table 10: Power Management**

| Name             | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain   | I/O<br>Reset     | I/O<br>Pwr off      | Description                                             |

|------------------|--------------|--------------|--------------|-------------------|------------------|---------------------|---------------------------------------------------------|

| BB_I_P           | B4           | -            | -            | VDD_IO /<br>VDD_C | Input            | Input               | Analog I Channel Differential Input                     |

| BB_I_N           | A4           | -            | -            | VDD_IO /<br>VDD_C | Input            | Input               | Analog I Channel Differential Input                     |

| BB_Q_P           | B5           | -            | -            | VDD_IO /<br>VDD_C | Input            | Input               | Analog Q Channel Differential Input                     |

| BB_Q_N           | A5           | -            | -            | VDD_IO /<br>VDD_C | Input            | Input               | Analog Q Channel Differential Input                     |

| BB_CLK_P         | А3           | -            | -            | VDD_IO /<br>VDD_C | Input            | Input               | Analog CLK Channel Differential Input                   |

| BB_CLK_N         | B3           | -            | -            | VDD_IO /<br>VDD_C | Input            | Input               | Analog CLK Channel Differential Input                   |

| BB_SLEEP_N       | A2           | -            | -            | VDD_IO            | Output<br>Low    | Input Pull-<br>down | Output RF Sleep                                         |

| PIOO /<br>BB_SDA | C4           | -            | -            | VDD_IO            | Input<br>Pull-up | Input<br>Pull-up    | I/O DDC for RF control Serial Data<br>Shared with PIO0  |

| PIO1 /<br>BB_SCL | D3           | -            | -            | VDD_IO            | Input<br>Pull-up | Input<br>Pull-up    | I/O DDC for RF control Serial Clock<br>Shared with PIO1 |

| RF_CLK_N         | -            | -            | 10           | VDD_ANA           | Output           | Output              | Analog CLK Differential Output                          |

| RF_CLK_P         | -            | -            | 9            | VDD_ANA           | Output           | Output              | Analog CLK Differential Output                          |

| RF_I_N           | -            | -            | 12           | VDD_ANA           | Output           | Output              | Analog I-Channel Differential Output                    |

| RF_I_P           | -            | -            | 11           | VDD_ANA           | Output           | Output              | Analog I-Channel Differential Output                    |

| RF_Q_N           | -            | -            | 14           | VDD_ANA           | Output           | Output              | Analog Q-Channel Differential Output                    |

| RF_Q_P           | -            | -            | 13           | VDD_ANA           | Output           | Output              | Analog Q-Channel Differential Output                    |

| RF_SCL           | -            | -            | 7            | VDD_RF            | Input            | Input               | I/O DDC for RF control Serial Clock                     |

| RF_SDA           | -            | -            | 8            | VDD_RF            | Input            | Input               | I/O DDC for RF control Serial Data                      |

| RF_SLEEP_N       | -            | -            | 6            | VDD_RF            | Input            | Input               | Input RF Sleep                                          |

Table 11: RF/BB interface

| Name     | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset | I/O<br>Pwr off | Description              |

|----------|--------------|--------------|--------------|-----------------|--------------|----------------|--------------------------|

| LNAIN    | -            | 56           | 24           | VDD_LNA         | Input        | Input          | LNA Input                |

| LNAOUT   | -            | 2            | 2            | VDD_LNA         | Output       | Output         | LNA Output               |

| MIX_IN_N | -            | 5            | 5            | VDD_ANA         | Input        | Input          | Mixer Differential Input |

| MIX_IN_P | -            | 4            | 4            | VDD_ANA         | Input        | Input          | Mixer Differential Input |

| XTAL_I   | -            | 49           | 17           | VDD_SYN         | Input        | Input          | XTO Input                |

| XTAL_O   | -            | 48           | 16           | VDD_SYN         | Output       | Output         | XTO Output               |

Table 12: RF Analog

| Name                  | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off     | Description                                                     |

|-----------------------|--------------|--------------|--------------|-----------------|------------------|--------------------|-----------------------------------------------------------------|

| RTC_XTAL_O            | B1           | 6            | -            | VDD_B           | Output           | Output             | Output RTC                                                      |

| RTC_XTAL_I            | A1           | 7            | -            | VDD_B           | Input            | Input              | Input RTC                                                       |

| TCK                   | A10          | 40           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Input JTAG Test Clock                                           |

| SAFEBOOT_N /<br>TDI   | C9           | 38           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Input JTAG Test Data In<br>Shared with Safe Boot Mode (Table 4) |

| TIMEPULSE /           | C8           | 39           | -            | VDD_IO          | Output           | Input              | Output JTAG Data Out                                            |

| TDO                   |              |              |              |                 | low              | Pull-up            | Shared with Time Pulse                                          |

| CFG_PIN /<br>TMS      | A8           | 43           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Input JTAG Test Mode Select<br>Shared with CFG_PIN (Table 5)    |

| VDCTEST               | -            | 3            | 3            |                 |                  |                    | Analog RF test pin                                              |

| PIO9 /<br>PER_RESET_N | G6           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Peripheral Reset<br>Shared with PIO9                     |

#### Table 13: System

| Name   | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset | I/O<br>Pwr off | Description             |

|--------|--------------|--------------|--------------|-----------------|--------------|----------------|-------------------------|

| USB_DM | J2           | 14           | -            | VDD_USB         | Input        | Input          | I/O Differential USB D- |

| USB_DP | K1           | 13           | -            | VDD_USB         | Input        | Input          | I/O Differential USB D+ |

#### Table 14: USB

| Name           | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off   | Description                                              |

|----------------|--------------|--------------|--------------|-----------------|------------------|------------------|----------------------------------------------------------|

| PIO2 /<br>SDA2 | Н8           | 33           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | I/O DDC for peripherals Serial Data<br>Shared with PIO2  |

| PIO3/<br>SCL2  | H10          | 34           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | I/O DDC for peripherals Serial Clock<br>Shared with PIO3 |

#### Table 15: DDC

| Name                             | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off   | Description                                                    |

|----------------------------------|--------------|--------------|--------------|-----------------|------------------|------------------|----------------------------------------------------------------|

| PIO4 /<br>RXD1                   | G7           | 24           | -            | VDD_IO          | Input<br>Pull-Up | Input<br>Pull-Up | Input UART 1 RxD<br>Shared with PIO4                           |

| PIO5 /<br>TXD1                   | H6           | 21           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Output UART 1 TxD<br>Shared with PIO5                          |

| PIO11/<br>ANT_OFF /<br>TXD2      | H2           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Output UART 2 TxD<br>Shared with ANT_OFF<br>Shared with PIO11  |

| PIO12/<br>ANT_SHORT_<br>N / RXD2 | G2           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input UART 2 RxD<br>Shared with ANT_SHORT<br>Shared with PIO12 |

Table 16: Asynchronous serial interface (UART)

| Name                          | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off   | Description                                                          |

|-------------------------------|--------------|--------------|--------------|-----------------|------------------|------------------|----------------------------------------------------------------------|

| PIO6<br>SS_N /<br>SCSO_N      | F8           | 20           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | I/O SPI Chip/Slave Select<br>Shared with PIO6                        |

| PIO19<br>CFG_COM0 /<br>MOSI   | J10          | 32           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | I/O SPI MOSI<br>Shared with CFG_COM0 (Table 7)<br>Shared with PIO19  |

| PIO20 /<br>CFG_COM1 /<br>MISO | K4           | 18           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | VO SPI MISO<br>Shared with CFG_COM1 (Table 7)<br>Shared with PIO20   |

| PIO21 /<br>CFG_GPS0 /<br>SCK  | K5           | 19           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | I/O SPI Clock<br>Shared with CFG_GPSO (Table 8)<br>Shared with PIO21 |

#### Table 17: SPI

| Name                                            | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off   | Description                                                                                              |

|-------------------------------------------------|--------------|--------------|--------------|-----------------|------------------|------------------|----------------------------------------------------------------------------------------------------------|

| PIO7 /<br>EXTINTO                               | D5           | 44           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input External Interrupt / Time Mark 0<br>Shared with PIO7                                               |

| PIO8 /<br>EXTINT1                               | D6           | 45           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input External Interrupt / Time Mark 1<br>Shared with PIO8                                               |

| TIMEPULSE /<br>TDO                              | C8           | 39           | -            | VDD_IO          | Output<br>low    | Input<br>Pull-up | Output Time Pulse<br>Shared with JTAG Test Data Out                                                      |

| PIO18 /<br>CFG_FFU3 /<br>EM_A21 /<br>TIMEPULSE2 | H4           | 16           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Output Time Pulse 2 Shared with EM_A21 on CVBGA Shared with CFG_FFU3 (for further use) Shared with PIO18 |

#### Table 18: External Interrupt / Time Mark

| Name                             | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off   | Description                                                                         |

|----------------------------------|--------------|--------------|--------------|-----------------|------------------|------------------|-------------------------------------------------------------------------------------|

| PIO10/<br>ANT_DETECT             | H1           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input Active Antenna Detection<br>Shared with PIO10                                 |

| PIO11/<br>ANT_OFF /<br>TXD2      | H2           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Output Active Antenna Off<br>Shared with UART 2 TxD<br>Shared with PIO11            |

| PIO12/<br>ANT_SHORT_<br>N / RXD2 | G2           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input Active Antenna Short Detection<br>Shared with UART 2 RxD<br>Shared with PIO12 |

#### Table 19: Antenna supervisor

| Name                                            | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off   | Description                                                                                             |

|-------------------------------------------------|--------------|--------------|--------------|-----------------|------------------|------------------|---------------------------------------------------------------------------------------------------------|

| PIO13 /<br>CFG_CLK0 /<br>EM_A0                  | В9           | 41           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_CLK0 (Table 6) Shared with EM_A0 on CVBGA Shared with PIO13                                   |

| PIO14 /<br>CFG_CLK1                             | F9           | 35           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_CLK1 (Table 6)<br>Shared with PIO14                                                           |

| PIO15 /<br>CFG_CLK2 /<br>EM_A18                 | F10          | 36           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_CLK2 (Table 6) Shared with EM_A18 on CVBGA Shared with PIO15                                  |

| PIO16 /<br>CFG_FFU0 /<br>EM_A19                 | E10          | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CGF_FFUO (for further use)<br>Shared with EM_A19<br>Shared with PIO 16                            |

| PIO17 /<br>CFG_FFU2 /<br>EM_A20                 | B10          | 37           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CGF_FFU2 (for further use)<br>Shared with EM_A20 on CVBGA<br>Shared with PIO17                    |

| PIO18 /<br>CFG_FFU3 /<br>EM_A21 /<br>TIMEPULSE2 | H4           | 16           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CGF_FFU3 (for further use) Shared with EM_A21 on CVBGA Shared with Time Pulse 2 Shared with PIO18 |

| PIO19 /<br>CFG_COM0 /<br>MOSI                   | J10          | 32           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_COM0 (Table 7)<br>Shared with SPI MOSI<br>Shared with PIO19                                   |

| PIO20 /<br>CFG_COM1 /<br>MISO                   | K4           | 18           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_COM1 (Table 7)<br>Shared with SPI MISO<br>Shared with PIO20                                   |

| PIO21 /<br>CFG_GPS0 /<br>SCK                    | K5           | 19           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_GPSO (Table 8)<br>Shared with SPI SCK<br>Shared with PIO21                                    |

| PIO22 /<br>CFG_GPS1                             | D2           | 11           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_GPS1 (Table 8) Shared with PIO22                                                              |

| PIO23 /<br>CFG_GPS2                             | C3           | 10           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_GPS2 (Table 8)<br>Shared with PIO23.                                                          |

| PIO24 /<br>CFG_FFU1                             | G10          | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_FFU0 (for further use)<br>Shared with PIO24                                                   |

| CFG_PIN /<br>TMS                                | A8           | 43           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input CFG_PIN (Table 5) Shared with JTAG Test Mode Select                                               |

| SAFEBOOT_N<br>/ TDI                             | C9           | 38           | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up | Input Safe Boot Mode (Table 4)<br>Shared with JTAG Test Data In                                         |

**Table 20: Configuration**

| Name                           | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off     | Description                                                                  |

|--------------------------------|--------------|--------------|--------------|-----------------|------------------|--------------------|------------------------------------------------------------------------------|

| EM_D0                          | G9           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D0                                                              |

| EM_D1                          | J6           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D1                                                              |

| EM_D2                          | K6           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D2                                                              |

| EM_D3                          | J5           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D3                                                              |

| EM_D4                          | F4           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D4                                                              |

| EM_D5                          | H5           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D5                                                              |

| EM_D6                          | G5           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D6                                                              |

| EM_D7                          | H9           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D7                                                              |

| EM_D8                          | A7           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D8                                                              |

| EM_D9                          | В7           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D9                                                              |

| EM_D10                         | E7           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D10                                                             |

| EM_D11                         | C2           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D11                                                             |

| EM_D12                         | J4           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D12                                                             |

| EM_D13                         | K3           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D13                                                             |

| EM_D14                         | F3           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D14                                                             |

| EM_D15                         | В6           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | I/O Data Bus D15                                                             |

| PIO13 /<br>CFG_CLK0 /<br>EM_A0 | B9           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Output Address Bus A0<br>Shared with CFG_CLK0 (Table 6)<br>Shared with PIO13 |

| EM_A1                          | D9           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A1                                                        |

| EM_A2                          | C10          | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A2                                                        |

| EM_A3                          | C7           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A3                                                        |

| EM_A4                          | E9           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A4                                                        |

| EM_A5                          | D7           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A5                                                        |

| EM_A6                          | A9           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A6                                                        |

| EM_A7                          | B8           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A7                                                        |

| EM_A8                          | G4           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A8                                                        |

| EM_A9                          | A6           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A9                                                        |

| EM_A10                         | E1           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A10                                                       |

| EM_A11                         | D1           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A11                                                       |

| Name                                            | Pin<br>CVBGA | Pin<br>MLF56 | Pin<br>MLF24 | Power<br>Domain | I/O<br>Reset     | I/O<br>Pwr off     | Description                                                                                              |

|-------------------------------------------------|--------------|--------------|--------------|-----------------|------------------|--------------------|----------------------------------------------------------------------------------------------------------|

| EM_A12                                          | E2           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A12                                                                                   |

| EM_A13                                          | J1           | -            | -            | VDD_IO          | Output<br>Iow    | Input<br>Pull-down | Output Address Bus A13                                                                                   |

| EM_A14                                          | F1           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A14                                                                                   |

| EM_A15                                          | F2           | -            | -            | VDD_IO          | Output<br>Iow    | Input<br>Pull-down | Output Address Bus A15                                                                                   |

| EM_A16                                          | G1           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A16                                                                                   |

| EM_A17                                          | НЗ           | -            | -            | VDD_IO          | Output<br>low    | Input<br>Pull-down | Output Address Bus A17                                                                                   |

| PIO15 /<br>CFG_CLK2 /<br>EM_A18                 | F10          | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Output Address Bus A18<br>Shared with CFG_CLK2 (Table 6)<br>Shared with PIO15                            |

| PIO16 /<br>CFG_FFU0 /<br>EM_A19                 | E10          | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Output Address Bus A19<br>Shared with CFG_FFUO (for further use)<br>Shared with PIO16                    |

| PIO17 /<br>CFG_FFU2 /<br>EM_A20                 | B10          | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Output Address Bus A20<br>Shared with CFG_FFU2 (for further use)<br>Shared with PIO17                    |

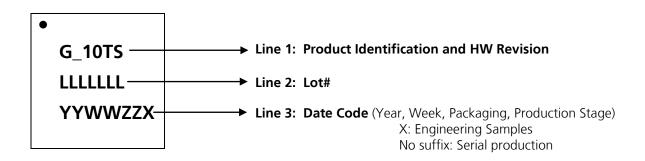

| PIO18 /<br>CFG_FFU3 /<br>EM_A21 /<br>TIMEPULSE2 | H4           | -            | -            | VDD_IO          | Input<br>Pull-up | Input<br>Pull-up   | Output Address Bus A21 Shared with Time Pulse 2 Shared with CFG_FFU3 (for further use) Shared with PIO18 |